**USER'S MANUAL**

**µPD70108**

**µPD70116**

NEC ELECTRONICS (EUROPE) GMBH

**USER'S MANUAL**

**μPD70108**

**μPD70116**

**3/85 V1.0**

VOLUME OF PAGE

Pages

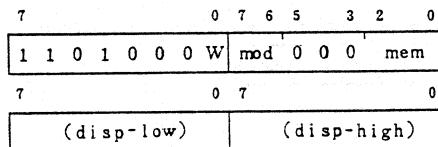

i - iv

| Chapter | Pages          |

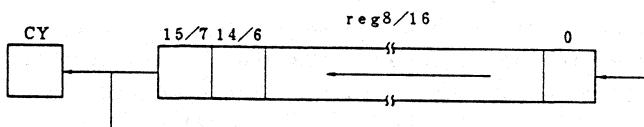

|---------|----------------|

| 1       | 10             |

| 2       | 12             |

| 3       | 8              |

| 4       | 7              |

| 5       | 5              |

| 6       | 11             |

| 7       | 4              |

| 8       | 1              |

| 9       | 4              |

| 10      | 11             |

| 11      | 4              |

| 12      | i - viii & 329 |

| 13      | 10             |

| A       | 3              |

| B       | 5              |

| TOTAL   | 436            |

## Table of Contents

|                                                                  | <u>Page</u> |

|------------------------------------------------------------------|-------------|

| <b>Chapter 1 General</b>                                         |             |

| 1.1 Features .....                                               | 1-2         |

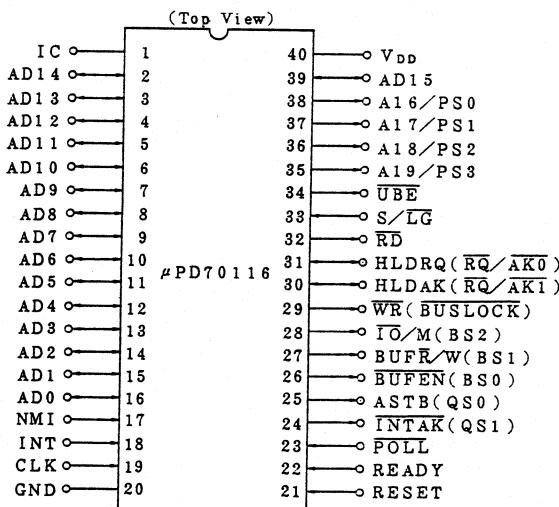

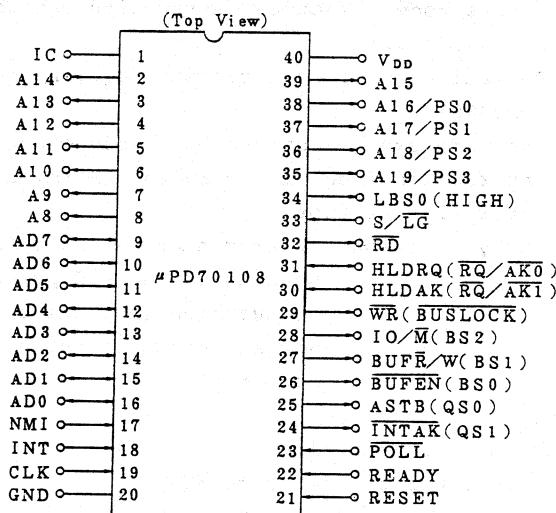

| 1.2 Pin Configuration of uPD70108/70116 .....                    | 1-4         |

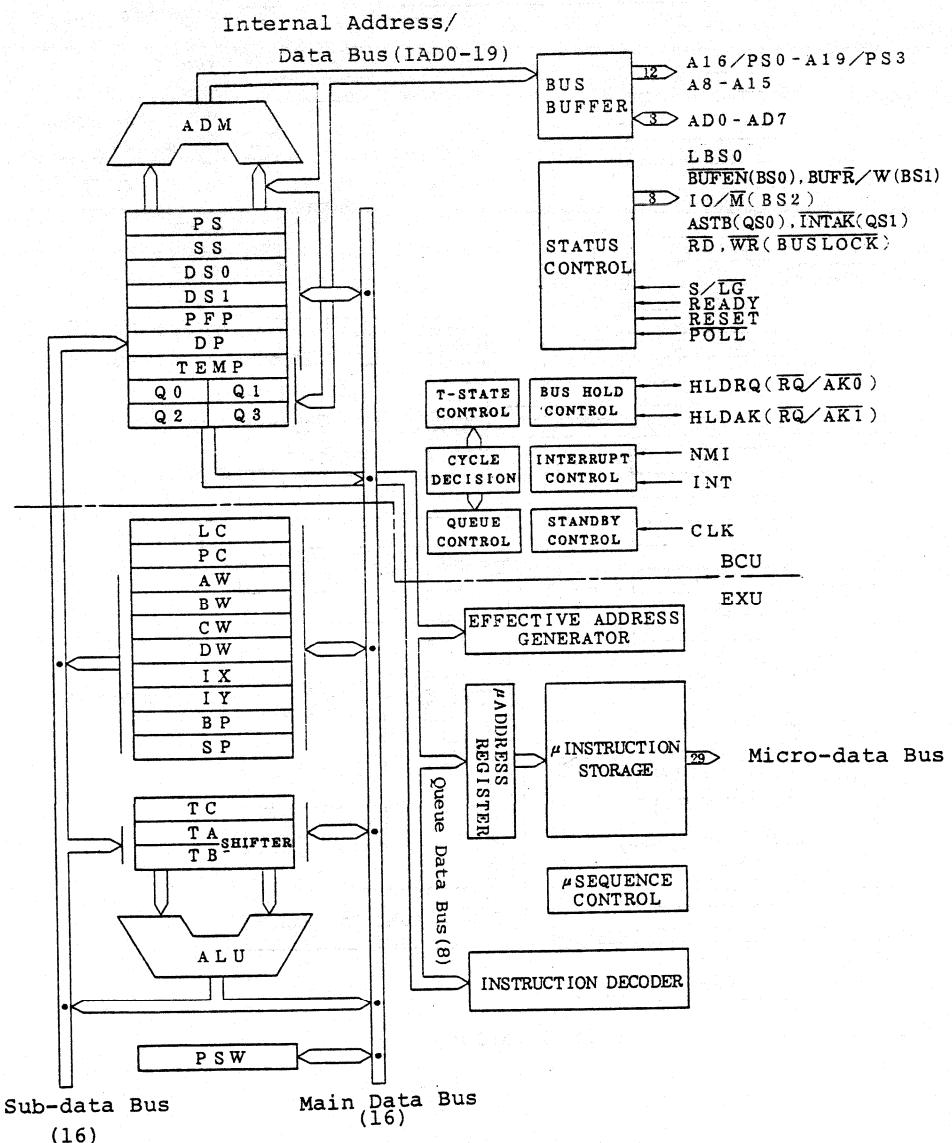

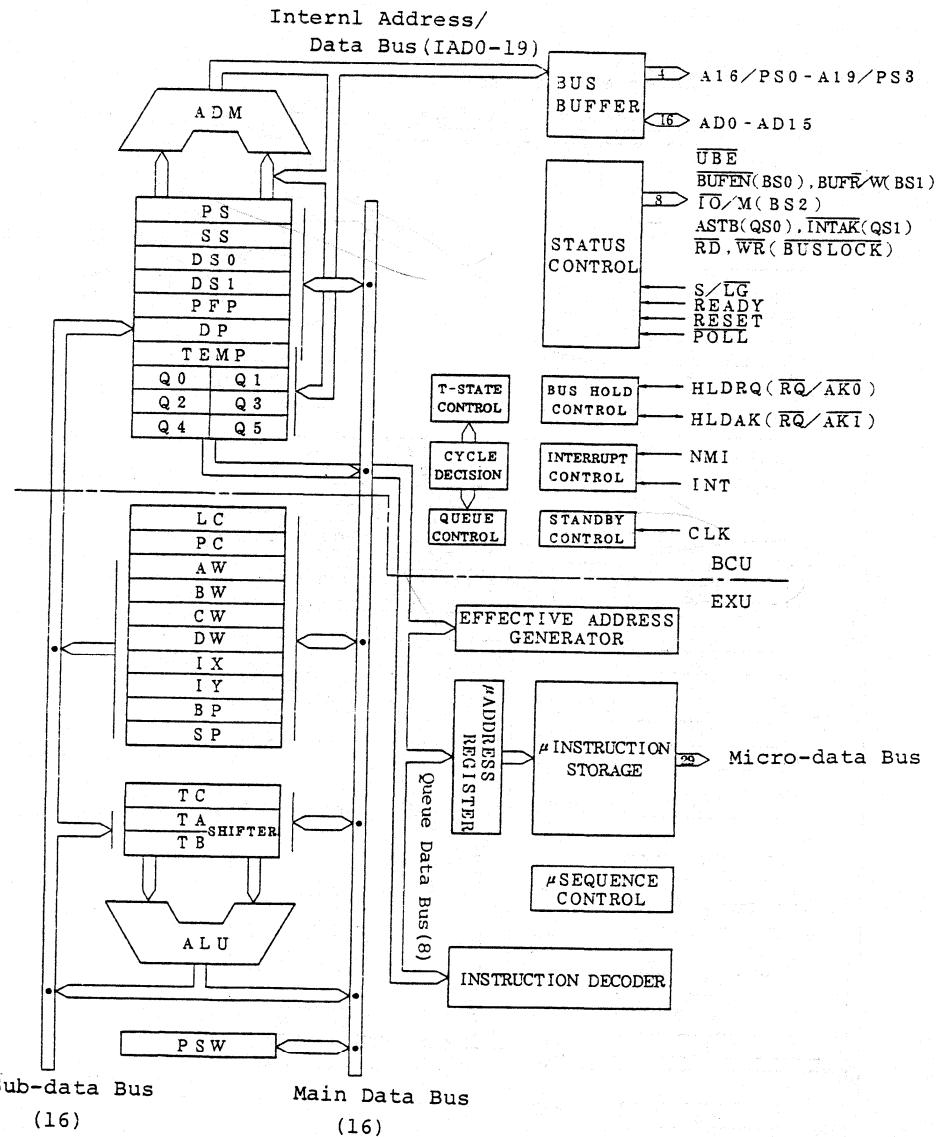

| 1.3 Block Diagram of uPD70108/70116 .....                        | 1-5         |

| <br><b>Chapter 2 Pin Functions</b>                               |             |

| 2.1 A15-A8 (Address Bus) .....                                   | 2-1         |

| 2.2 AD7-AD0 (Address/Data Bus) .....                             | 2-1         |

| 2.3 AD15-AD0 (Address/Data Bus) .....                            | 2-2         |

| 2.4 NMI (Nonmaskable Interrupt) .....                            | 2-3         |

| 2.5 INT (Maskable Interrupt) .....                               | 2-3         |

| 2.6 CLK (Clock) .....                                            | 2-3         |

| 2.7 RESET (Reset) .....                                          | 2-4         |

| 2.8 READY (Ready) .....                                          | 2-4         |

| 2.9 <u>POLL</u> (Poll) .....                                     | 2-4         |

| 2.10 <u>RD</u> (Read Strobe) .....                               | 2-4         |

| 2.11 S/ <u>LG</u> (Small/Large) .....                            | 2-5         |

| 2.12 <u>INTAK</u> (Interrupt Acknowledge) .....                  | 2-5         |

| 2.13 ASTB (Address Strobe) .....                                 | 2-6         |

| 2.14 <u>BUFEN</u> (Buffer Enable) .....                          | 2-6         |

| 2.15 BUFR/W (Buffer Read/Write) .....                            | 2-6         |

| 2.16 IO/ <u>M</u> (IO/Memory) .....                              | 2-6         |

| 2.17 <u>IO/M</u> (IO/Memory) .....                               | 2-7         |

| 2.18 <u>WR</u> (Write Strobe) .....                              | 2-7         |

| 2.19 <u>HLDACK</u> (Hold Acknowledge) .....                      | 2-7         |

| 2.20 <u>HLDREQ</u> (Hold Request) .....                          | 2-7         |

| 2.21 LBS0 (Latched Bus Status 0) .....                           | 2-8         |

| 2.22 <u>UBE</u> (Upper Byte Enable) .....                        | 2-8         |

| 2.23 A19/PS3 - A16/PS0<br>(Address Bus/Processor Status) .....   | 2-9         |

| 2.24 QS1, QSO (Queue Status) .....                               | 2-10        |

| 2.25 BS2-BS0 (Bus Status) .....                                  | 2-11        |

| 2.26 <u>BUSLOCK</u> (Bus Lock) .....                             | 2-11        |

| 2.27 <u>RQ/AK1</u> , <u>AK0</u> (Hold Request/Acknowledge) ..... | 2-12        |

|                                      | <u>Page</u> |

|--------------------------------------|-------------|

| 2.28 VDD (Power Supply) .....        | 2-12        |

| 2.29 GND (Ground) .....              | 2-12        |

| 2.30 IC (Internally Connected) ..... | 2-12        |

### Chapter 3 Functions of Internal Block

|                                                             |     |

|-------------------------------------------------------------|-----|

| 3.1 Program Counter (PC) .....                              | 3-2 |

| 3.2 Prefetch Pointer (PFP) .....                            | 3-2 |

| 3.3 Q0 - Q3/Q0 - Q5 (Prefetch Queue) .....                  | 3-2 |

| 3.4 DP (Data Pointer) .....                                 | 3-3 |

| 3.5 TEMP (Temporary Communication Register) .....           | 3-3 |

| 3.6 Segment Registers (PS, SS, DS0, and DS1) .....          | 3-3 |

| 3.7 ADM (Address Modifier) .....                            | 3-4 |

| 3.8 General-Purpose Registers<br>(AW, BW, CW, and DW) ..... | 3-4 |

| 3.9 Pointers (SP, BP)<br>and Index Registers (IX, IY) ..... | 3-5 |

| 3.10 TA/TB (Temporary Register/Shifter A,B) .....           | 3-5 |

| 3.11 TC (Temporary Register C) .....                        | 3-6 |

| 3.12 ALU (Arithmetic Logic Unit) .....                      | 3-6 |

| 3.13 Program Status Word (PSW) .....                        | 3-6 |

| 3.14 LC (Loop Counter) .....                                | 3-7 |

| 3.15 EAG (Effective Address Generator) .....                | 3-8 |

| 3.16 Instruction Decoder .....                              | 3-8 |

| 3.17 Microaddress register .....                            | 3-8 |

| 3.18 Microinstruction ROM .....                             | 3-8 |

| 3.19 Microinstruction sequence circuit .....                | 3-8 |

### Chapter 4 Configuration of Memory and Input/Output

|                                           |     |

|-------------------------------------------|-----|

| 4.1 Memory Configuration and Access ..... | 4-1 |

| 4.2 I/O Configuration and Accessing ..... | 4-6 |

### Chapter 5 Read/Write Timing of Memory and Input/Output

### Chapter 6 Interrupts

|                          |     |

|--------------------------|-----|

| 6.1 INT Interrupts ..... | 6-3 |

|--------------------------|-----|

|                                                                            | <u>Page</u> |

|----------------------------------------------------------------------------|-------------|

| 6.2 BRK Flag (Single-Step) Interrupt .....                                 | 6-8         |

| 6.3 Timing That Does Not Accept Interrupts .....                           | 6-9         |

| 6.4 Interrupt Process During Block Transfer<br>Instruction Execution ..... | 6-10        |

#### Chapter 7 Standby Function

|                                                                 |     |

|-----------------------------------------------------------------|-----|

| 7.1 Setting Standby Mode .....                                  | 7-1 |

| 7.2 Standby Mode .....                                          | 7-1 |

| 7.3 Releasing Standby Mode by<br>External Interrupt Input ..... | 7-3 |

| 7.4 Releasing Standby Mode by RESET Input .....                 | 7-4 |

#### Chapter 8 Reset Operation

#### Chapter 9 Logical and Physical Addresses

#### Chapter 10 Addressing

|                                   |      |

|-----------------------------------|------|

| 10.1 Instruction Address .....    | 10-1 |

| 10.2 Memory Operand Address ..... | 10-4 |

#### Chapter 11 Implementation of Faster Execution

|                                                               |      |

|---------------------------------------------------------------|------|

| 11.1 Dual Data Bus Method .....                               | 11-2 |

| 11.2 Effective Address Generator .....                        | 11-3 |

| 11.3 16/32-Bit Temporary Registers/Shifters<br>(TA, TB) ..... | 11-3 |

| 11.4 Loop Counter (LC) .....                                  | 11-4 |

| 11.5 PC and PFP .....                                         | 11-4 |

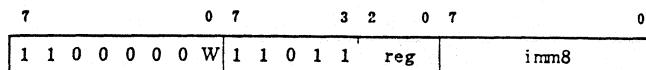

#### Chapter 12 Instructions

|                                                  |       |

|--------------------------------------------------|-------|

| 12.1 Data Transfer Instructions .....            | 12-1  |

| 12.2 Repeat Prefix .....                         | 12-21 |

| 12.3 Primitive Block Transfer Instructions ..... | 12-28 |

| 12.4 Bit Field Manipulation Instructions .....   | 12-38 |

| 12.5 Input/Output Instructions .....             | 12-46 |

|                                                | <u>Page</u> |

|------------------------------------------------|-------------|

| 12.6 Primitive Input/Output Instructions ..... | 12-50       |

| 12.7 Addition/Subtracion Instructions .....    | 12-54       |

| 12.8 BCD Operation Instruction .....           | 12-79       |

| 12.9 Increment/Decrement Instructions .....    | 12-89       |

| 12.10 Multiplication Instructions .....        | 12-95       |

| 12.11 Division Instructions .....              | 12-111      |

| 12.12 BCD Adjust Instructions .....            | 12-127      |

| 12.13 Data Conversion Instructions .....       | 12-131      |

| 12.14 Comparison Instructions .....            | 12-135      |

| 12.15 Complement Operation Instructions .....  | 12-141      |

| 12.16 Logical Operation Instructions .....     | 12-145      |

| 12.17 Bit Manipulation Instructions .....      | 12-172      |

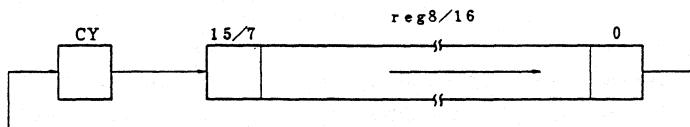

| 12.18 Shift Instructions .....                 | 12-209      |

| 12.19 Rotate Instructions .....                | 12-227      |

| 12.20 Subroutine Control Instructions .....    | 12-251      |

| 12.21 Push Instructions .....                  | 12-260      |

| 12.22 Branch Instructions .....                | 12-276      |

| 12.23 Load and Branch Instructions .....       | 12-282      |

| 12.24 Break Instructions .....                 | 12-302      |

| 12.25 CPU Control Instructions .....           | 12-313      |

| 12.26 Segment Override Prefix .....            | 12-325      |

| 12.27 Emulation Mode Instructions .....        | 12-326      |

### Chapter 13 uPD8080AF Emulation

|                                               |      |

|-----------------------------------------------|------|

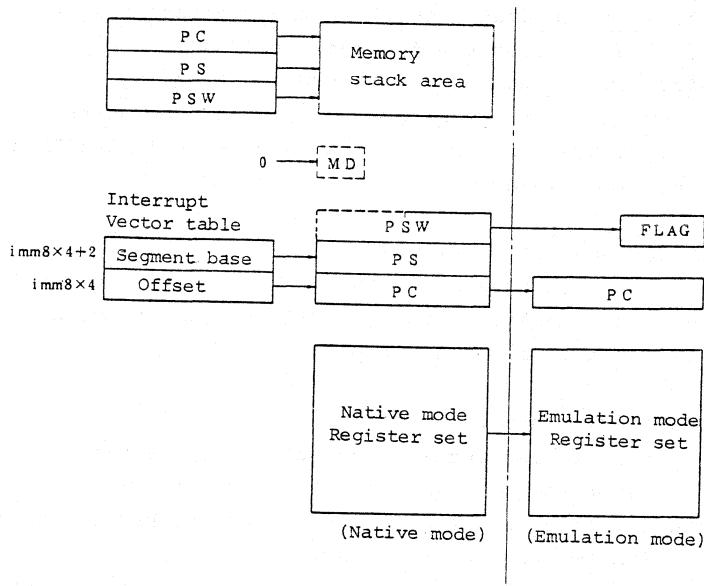

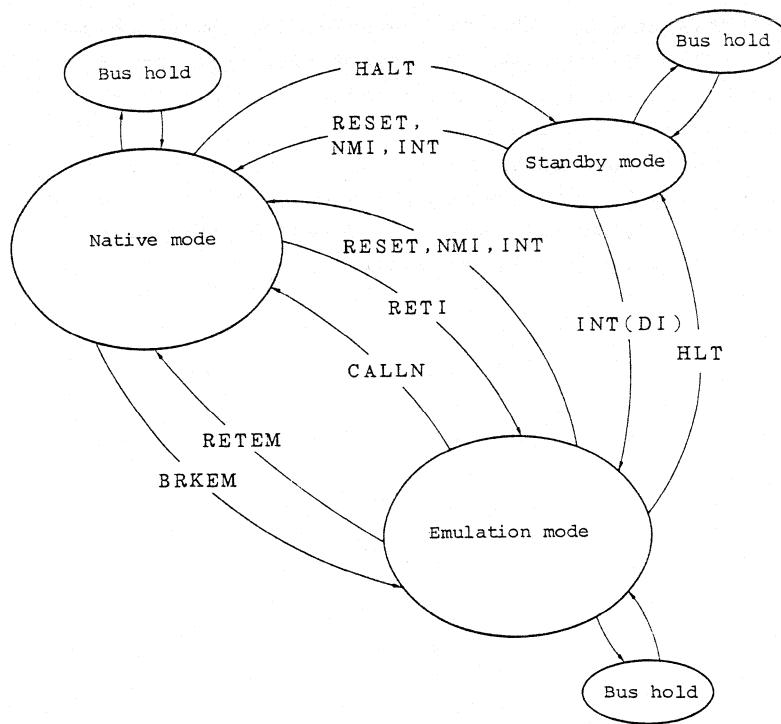

| 13.1 From Native to Emulation Mode .....      | 13-1 |

| 13.2 From Emulation Mode to Native Mode ..... | 13-4 |

| 13.3 Emulation Mode .....                     | 13-7 |

Appendix A List of uPD70108/70116 Instruction Mnemonics A-1

Appendix B Index of uPD70108/70116 Instructions

(In Alphabetical Order) ..... B-1

Appendix C Instruction Set ..... C-1

## Chapter 1 General

The uPD70108/70116 is a CMOS 8/16-bit microprocessor provided with 8/16-bit architecture and an 8-bit data bus. The uPD70108/70116 has a powerful instruction set including bit processing, packed multi-digit BCD operations, high-speed multiplication/division operations, and variable bit field operations, realizing flexible processes of various applications at high speeds. As one of the features this microprocessor offers, the hardware incorporates a multiplication/division circuit and an effective address generator. Additionally, an internal dual bus system is employed.

The uPD70108/70116 also has emulation functions of an uPD8080AF and comes with a standby mode that significantly reduces power consumption. The uPD70108 and uPD70116 are software-compatible with one another.

This document introduces a new product, still under development, and its functions. The descriptions are therefore subject to change without advance notice.

## 1.1 Features

- (1) 8-bit bus microprocessor: uPD70108

- (2) 16-bit bus microprocessor: uPD70116

- (3) Minimum instruction execution time: 400 ns

(at 5MHz/5V)

- (4) Maximum addressable memory: 1M byte

- (5) Abundant memory addressing modes

- (6) 14- x 16-bit register set

- (7) 101 instructions

- (8) Bit field operation instructions: Data transfer

between 1- to 16-bit fields of the memory and

accumulator

- (9) Packed BCD operation instruction: Addition,

subtraction, and comparison of 1- to 255-digit BCD

strings

- (10) High-speed multiplication/division instruction

(exclusive hardware is incorporated): 6 to 8 us

(at 5MHz/5V)

- (11) Inter-memory high-speed block transfer:

uPD70108: 625K bytes/sec (at 5MHz/5V)

uPD70116: 625K words/sec (at 5MHz/5V)

- (12) Bit operation instruction: 8- or 16-bit register

Any bit of the memory can

be set, cleared, inverted,

and tested.

- (13) High-speed calculation of effective addresses:

Exclusive hardware is incorporated.

- (14) Abundant interrupt processing functions:

External interrupt: NMI (non-maskable interrupt),

INT (maskable interrupt)

Interrupt by software: BRK (unconditional)

BRKV (when V=1)

BRKEN (emulation)

CHKIND (array index check)

CALLN (native routine call)

- (15) IEEE-796 bus-compatible interface

- (16) Two operation modes

- Native mode: executes instruction set of uPD70108/70116.

- Emulation mode: executes instruction set of uPD8080AF.

- The mode can be changed by a mode-change instruction (such as BRKEM and RETEM) and an external interrupt.

- (17) Standby function: Program standby (halt function)

Results in reduced power consumption (approximately 1/10 of normal operating current consumption.)

- (18) CMOS

- (19) Low power consumption

- (20) Single power source: 3 to 6V

- (21) 5MHz clock: duty cycle 50%

- (22) 40-pin plastic DIP

## 1.2 Pin Configuration of uPD70108/70116

### 1.3 uPD70108/70116 Block Diagram

uPD70108 Block Diagram

uPD70116 Block Diagram

#### 1.4 uPD70108 Pin Identification

| No.  | Symbol              | Direction | Function                                                    |

|------|---------------------|-----------|-------------------------------------------------------------|

| 1    | IC                  | -         | Internally Connected                                        |

| 2-8  | A14-A8              | Out       | Address Bus, Middle Bits                                    |

| 9-16 | AD7-AD0             | In/Out    | Address/Data Bus                                            |

| 17   | NMI                 | In        | Nonmaskable Interrupt Input                                 |

| 18   | INT                 | In        | Maskable Interrupt Input                                    |

| 19   | CLK                 | In        | Clock Input                                                 |

| 20   | GND                 | -         | Ground Potential                                            |

| 21   | RESET               | In        | Reset Input                                                 |

| 22   | READY               | In        | Ready Input                                                 |

| 23   | <u>POLL</u>         | In        | Poll Input                                                  |

| 24   | <u>INTAK</u> (QS1)  | Out       | Interrupt Acknowledge Output<br>(Queue Status Bit 1 Output) |

| 25   | ASTB (QS0)          | Out       | Address Strobe Output (Queue<br>Status Bit 0 Output)        |

| 26   | <u>BUFEN</u> (BS0)  | Out       | Buffer Enable Output (Bus Status<br>Bit 0 Output)           |

| 27   | <u>BUFR/W</u> (BS1) | Out       | Buffer Read/Write Output (Bus<br>Status Bit 1 Output)       |

| 28   | IO/ <u>M</u> (BS2)  | Out       | Access is I/O or Memory (Bus<br>Status Bit 2 Output)        |

|       |                                              |                 |                                                                       |

|-------|----------------------------------------------|-----------------|-----------------------------------------------------------------------|

| 29    | <u>WR</u> ( <u>BUSLOCK</u> )                 | Out             | Write Strobe Output (Bus Lock Output)                                 |

| 30    | HLD <sub>AK</sub> ( <u>RQ</u> / <u>AK1</u> ) | Out<br>(In/Out) | Hold Acknowledge Output (Bus Hold Request Input/Acknowledge Output 1) |

| 31    | HLD <sub>RQ</sub> ( <u>RQ</u> / <u>AK0</u> ) | In<br>(In/Out)  | Hold Request Input (Bus Hold Request Input/Acknowledge Output 0)      |

| 32    | <u>RD</u>                                    | Out             | Read Strobe output                                                    |

| 33    | S/ <u>LG</u>                                 | In              | Small-scale/Large-scale System Input                                  |

| 34    | LBS0 (HIGH)                                  | In              | Latched Bus Status Input 0 (Always High in Large-scale Systems)       |

| 35-38 | A19/PS3 - A16/PS0                            | Out             | Address Bus, High Bits or Processor Status Output                     |

| 39    | A15                                          | Out             | Address Bus, Bit 15                                                   |

| 40    | VDD                                          | -               | Power Supply                                                          |

Note: Where pins have different functions in small- and large-scale systems, the large-scale system pin name and function are in parentheses.

### 1.5 uPD70116 Pin Identification

| No.  | Symbol              | Direction | Function                                                    |

|------|---------------------|-----------|-------------------------------------------------------------|

| 1    | IC                  | -         | Internally Connected                                        |

| 2-8  | AD14-AD8            | In/Out    | Address/Data Bus                                            |

| 9-16 | AD7-AD0             | In/Out    | Address/Data Bus                                            |

| 17   | NMI                 | In        | Nonmaskable Interrupt Input                                 |

| 18   | INT                 | In        | Maskable Interrupt Input                                    |

| 19   | CLK                 | In        | Clock Input                                                 |

| 20   | GND                 | -         | Ground Potential                                            |

| 21   | RESET               | In        | Reset Input                                                 |

| 22   | READY               | In        | Ready Input                                                 |

| 23   | <u>POLL</u>         | In        | Poll Input                                                  |

| 24   | <u>INTAK</u> (QS1)  | Out       | Interrupt Acknowledge Output<br>(Queue Status Bit 1 Output) |

| 25   | ASTB (QS0)          | Out       | Address Strobe Output (Queue Status Bit 0 Output)           |

| 26   | <u>BUFEN</u> (BS0)  | Out       | Buffer Enable Output (Bus Status Bit 0 Output)              |

| 27   | <u>BUFR/W</u> (BS1) | Out       | Buffer Read/Write Output (Bus Status Bit 1 Output)          |

| 28   | <u>IO/M</u> (BS2)   | Out       | Access is I/O or Memory (Bus Status Bit 2 Output)           |

|       |                                     |                 |                                                                       |

|-------|-------------------------------------|-----------------|-----------------------------------------------------------------------|

| 29    | <u>WR</u> ( <u>BUSLOCK</u> )        | Out             | Write Strobe Output (Bus Lock Output)                                 |

| 30    | HLD <sub>AK</sub> ( <u>RQ/AK1</u> ) | Out<br>(In/Out) | Hold Acknowledge Output (Bus Hold Request Input/Acknowledge Output 1) |

| 31    | HLD <sub>RQ</sub> ( <u>RQ/AK0</u> ) | In<br>(In/Out)  | Hold Request Input (Bus Hold Request Input/Acknowledge Output 0)      |

| 32    | <u>RD</u>                           | Out             | Read Strobe output                                                    |

| 33    | S/ <u>LG</u>                        | In              | Small-scale/Large-scale System Input                                  |

| 34    | <u>UBE</u>                          | In              | Upper Byte Enable                                                     |

| 35-38 | A19/PS3-A16/PS0                     | Out             | Address Bus, High Bits or Processor Status Output                     |

| 39    | AD15                                | In/Out          | Address/Data Bus                                                      |

| 40    | VDD                                 | -               | Power Supply                                                          |

Note: Where pins have different functions in small- and large-scale systems, the large-scale system pin name and function are in parentheses.

## Chapter 2 Pin Functions

This chapter describes the function of each uPD70108/70116 pin. Unless otherwise specified, these descriptions are applicable to both the uPD70108 and the uPD70116.

Because the bus width of the uPD70108 and uPD70116 are not the same, each microprocessor uses the bus for both address and data in its own particular way.

Moreover, the memory identification signals for the two microprocessors also are different; the uPD70108 uses an  $\overline{IO/M}$  signal while the uPD70116 uses an  $\overline{IO/M}$  signal. Some pins of both microprocessors are exclusively used depending on whether the microprocessors are mounted in a small- or large-scale system. Other pins function in either system.

2.1 A15-A8 (Address Bus) ... For small- and large-scale systems

(This description applies to the uPD70108 only)

The CPU uses these pins to output the middle 8 bits of the 20-bit address information. They are three-state output and become high impedance during hold acknowledge.

2.2 AD7-AD0 (Address/Data Bus) ... For small- and large-scale systems

(This description applies to the uPD70108 only)

The CPU uses these pins as the time multiplexed address and data bus. They output the lower 8 bits of the 20-bit address information and 8-bit data.

Input/Output operation of 16-bit data is performed in two steps. The low byte is sent first, followed by the high byte. These pins are three-state I/O and become high impedance during hold and interrupt acknowledge.

2.3 AD15-AD0 (Address/Data Bus) ... For small- and large scale systems.

(This description applies to the uPD70116 only)

The AD15-AD0 is a time-multiplexed Address/Data bus. This performs output of lower 16 bits of 20 bits address information and input/output of byte or word data. The uPD70116 locates memory and I/O operand to a byte-data bank to be accessed with even address (AD0=0) and a byte-data bank to be accessed with odd address (AD0=1). The LSB(AD0) has no meaning as a word data address but used for selecting the odd or even address bank. The UBE (Upper Byte Enable) signal is provided to access byte/word data besides AD0. This is used as the combination of the following table.

| Operand              | UBE | AD0 | No. of Bus Cycle |

|----------------------|-----|-----|------------------|

| Word of Even Address | 0   | 0   | 1                |

| Word of Odd Address  | 0   | 1*  | 2                |

|                      | 1   | 0** |                  |

| Byte of Even Address | 1   | 0   | 1                |

| Byte of Odd Address  | 0   | 1   | 1                |

\*: First Time \*\*: Second Time

A word operand in odd address is performed via two consecutive access of odd-byte bank and even-byte bank. In this case, first AD0=1 showing odd bank address is output, and second AD0=1 showing continuous even bank address is output automatically. These outputs are held to high or low level in the standby mode. These are 3-state output and becomes high impedance in the hold acknowledge and interrupt acknowledge states.

2.4 NMI (Nonmaskable Interrupt) ... For small- and large-scale systems

This pin is used to input nonmaskable interrupt requests. NMI cannot be masked by software. This input is active at the rising edge of a signal and can be sensed during any clock cycle. Actual interrupt processing begins, however, after completion of the instruction in progress.

The contents of interrupt vector 2 determines the starting address for the interrupt-servicing routine. Note that a hold request will be accepted even during NMI acknowledge.

This interrupt can be used to release the standby mode.

2.5 INT (Maskable Interrupt) ... For small- and large-scale systems

This pin is used to input an interrupt request that can be masked by software.

This input is active high level and is sensed during the last clock of the instruction. The interrupt will be accepted if the system is in interrupt enable state (if the interrupt enable flag (IE) is set). The CPU outputs the INTAK signal to inform external devices whether the interrupt request has been acknowledged.

The priority of interrupts is shown below. If NMI and INT interrupts occur at the same time, NMI has priority and INT can not be accepted. A hold request will be accepted even during INT acknowledge.

INT < NMI

This interrupt can be used to release the standby mode.

2.6 CLK (Clock) ... For small- and large-scale systems

This pin is used for external clock input.

## 2.7 RESET (Reset) ... For small- and large-scale systems

This pin is used to input the CPU reset signal, which is active high level. Input of this signal has priority over all other operations. After the reset signal input returns to low level the CPU begins execution of the program starting at address FFF0H.

In addition to the use during normal CPU start, the RESET input can be used to release the standby mode.

## 2.8 READY (Ready) ... For small- and large-scale systems

READY indicates that the data transfer is completed. When the signal goes high during read cycle, the data is latched one clock cycle later and the bus cycle terminated.

When the signal goes high during write cycle, the bus cycle is terminated.

## 2.9 POLL (Poll) . . . For small- and large-scale systems

The CPU checks the input at this pin by the execution of the POLL instruction. If the input is low level, execution continues. If the input is high level, the CPU will check the POLL input every five clock cycles until the input becomes low again.

These functions are used to synchronize CPU program execution with the operation of external devices.

## 2.10 RD (Read Strobe) ... For small- and large-scale systems

The CPU outputs this strobe signal during data read from an I/O device or memory. The IO/M signal is used to select between I/O and memory. This pin's output is three state and becomes high impedance during hold acknowledge.

## 2.11 S/LG (Small/Large) ... For small- and large-scale systems

This signal determines the operation mode of the CPU. This signal is fixed at either high or low level. When this signal is high level, the CPU will operate in small-scale system mode, and when low level, in large-scale system mode.

Pins 24 to 31 and pin 34 function differently depending on the operating mode of the CPU. Separate nomenclature is adopted for these signals in the two operation modes.

| Pin | Function           |                |

|-----|--------------------|----------------|

| No. | S/LG- high         | S/LG-low       |

| 24  | <u>INTAK</u>       | QS1            |

| 25  | ASTB               | QS0            |

| 26  | <u>BUFEN</u>       | BS0            |

| 27  | <u>BUFR/W</u>      | BS1            |

| 28  | <u>IO/M, IO/M</u>  | BS2            |

| 29  | <u>WR</u>          | <u>BUSLOCK</u> |

| 30  | HLD <sub>A</sub> K | <u>RQ/AK1</u>  |

| 31  | HLD <sub>R</sub> Q | <u>RQ/AK0</u>  |

| 34  | LBS0               | Always high    |

Note 1. IO/M for uPD70108. IO/M for uPD70116.

2. LBS0 for uPD70108.

## 2.12 INTAK (Interrupt Acknowledge) ... For small-scale systems

The CPU asserts the INTAK signal active low when it accepts an INT signal.

The external device synchronizes with this signal and outputs the interrupt vector to the CPU via the data bus (AD7-AD0). This output is held to high level in the standby mode.

2.13 ASTB (Address Strobe) ... For small-scale systems

The CPU outputs this strobe signal to latch address information at an external latch.

This output is held to high level in the standby mode.

2.14 BUFEN (Buffer Enable) ... For small-scale systems

This is used as the output enable signal for an external bidirectional buffer. The CPU outputs this signal during data transfer operations with an external memory or I/O device or during input of a interrupt vector.

This output is held to high level in the standby mode.

2.15 BUFR/W (Buffer Read/Write) ... For small-scale systems

The output of this signal determines the direction of data transfer with an external bidirectional buffer. A high output specifies transmission from the CPU to the external device, while a low signal specifies reception from the external device to the CPU.

This output is held to high or low level in the standby mode.

2.16 IO/M (IO/Memory) ... For small-scale systems

(This description applies to the uPD70108 only)

The CPU outputs this signal to specify either I/O access or memory access. A high-level output specifies I/O access and a low-level signal specifies memory access.

This output is held to high or low level in the standby mode.

The output from this pin is three state and becomes high impedance during hold acknowledge.

2.17  $\overline{IO/M}$  (IO/Memory) ... For small-scale systems

(This description applies to uPD70116 only)

The CPU outputs this signal to specify either I/O access or memory access. A low-level output specifies I/O access and a high-level signal specifies memory access.

This output is held to high or low level in the standby mode.

The output from this pin is three state and becomes high impedance during hold acknowledge.

2.18  $\overline{WR}$  (Write Strobe) ... For small-scale systems

The CPU outputs this strobe signal during data write to an I/O device or memory. Selection of either I/O or memory is performed by the  $IO/M$  signal.

This output is held to high level in the standby mode.

This pin's output is three state and becomes high impedance during hold acknowledge.

2.19  $HLD<sub>AK</sub>$  (Hold Acknowledge) ... For small-scale systems

This pin outputs an acknowledge signal to indicate when the CPU accepts a hold request signal ( $HLD<sub>RQ</sub>$ ). While this signal is active (high level), the address bus, address/data bus, and the control lines become high impedance.

2.20  $HLD<sub>RQ</sub>$  (Hold Request) ... For small-scale systems

This signal is input from external devices to request the CPU to release the address bus, address/data bus, and the control bus.

2.21 LBS0 (Latched Bus Status 0) ... For small-scale system

(This description applies to the uPD70108 only)

The CPU uses this signal along with the IO/M and BUFR/W signals to inform an external device what the current bus cycle is.

| IO/M BUFR/W | LBS0 | Bus Cycle             |

|-------------|------|-----------------------|

| 0           | 0    | Program fetch         |

| 0           | 1    | Memory read           |

| 1           | 0    | Memory write          |

|             | 1    | Passive state         |

| 0           | 0    | Interrupt acknowledge |

| 1           | 1    | I/O read              |

| 1           | 0    | I/O write             |

|             | 1    | Halt                  |

2.22 UBE (Upper Byte Enable) ... For small- and large scale systems

(This description applies to uPD70116 only)

This output indicates the using of the upper 8 bits (AD15-AD8) of the Address/Data bus during T2-T4 of bus cycle. This signal is active low and output during T1-T4 of the bus cycle. Bus cycles in which the UBE is active are shown in the following table.

| Operand              | UBE | AD0 | No.of Bus Cycle |

|----------------------|-----|-----|-----------------|

| Word of Even Address | 0   | 0   | 1               |

| Word of Odd Address  | 0   | 1*  | 2               |

|                      | 1   | 0** |                 |

| Byte of Even Address | 1   | 0   | 1               |

| Byte of Odd Address  | 0   | 1   | 1               |

\*: First Time

\*\*: Second Time

The UBE signal goes low level continuously during interrupt acknowledge state (because of necessity of word access of even address for vector read).

This signal is held to high level in the standby mode. The UBE is 3-state output and becomes high impedance during hold acknowledge.

#### 2.23 A19/PS3 - A16/PS0 (Address Bus/Processor Status) ... For small- and large-scale systems

These pins are time multiplexed to operate as an address bus and for output of processor status signals.

When used as the address bus, these pins output the high 4 bits of the 20-bit memory address. During I/O access, all 4 bits output data 0.

The processor status signals are output for both memory and I/O access. PS3 is always 0 in the native mode and always 1 in the emulation mode. The contents of the interrupt enable flag (IE) are output to PS2. PS1 and PS0 indicate which memory segment is being accessed.

| A17/PS1 | A16/PS0 | Segment         |

|---------|---------|-----------------|

| 0       | 0       | Data segment 1  |

| 0       | 1       | Stack segment   |

| 1       | 0       | Program segment |

| 1       | 1       | Data segment 0  |

The output of these pins are three state and becomes high impedance during hold acknowledge.

## 2.24 QS1, QS0 (Queue Status) ... For large-scale systems

The CPU uses these signals to inform external devices, such as the floating point arithmetic processor chip, about the status of the internal CPU instruction queue.

| QS1 | QS0 | Instruction queue status     |

|-----|-----|------------------------------|

| 0   | 0   | NOP (Queue does not operate) |

| 0   | 1   | First byte of instruction    |

| 1   | 0   | Queue empty                  |

| 1   | 1   | Subsequent byte              |

The instruction queue status indicated by these signals is the status when the execution unit (EXU) accesses the instruction queue. The data output from these pins are therefore valid only for one clock cycle immediately following queue access. These status signals are provided so that the floating point operation chip can monitor the CPU's program execution status and synchronize its operation with the CPU when control is passed to it by the FPO (Floating Point Operation) instruction.

These outputs are held to low level in the standby mode.

## 2.25 BS2-BS0 (Bus Status) ... For large-scale systems

The CPU uses these status signals to inform an external bus controller what the current bus cycle is. The external bus controller decodes these signals and generates the control signals required to perform access of the memory or I/O device.

| BS2 | BS1 | BS0 | Bus cycle             |

|-----|-----|-----|-----------------------|

|     | 0   | 0   | Interrupt acknowledge |

| 0   |     | 1   | I/O read              |

|     | 1   | 0   | I/O write             |

|     |     | 1   | Halt                  |

|     | 0   | 0   | Program fetch         |

| 1   |     | 1   | Memory read           |

|     | 1   | 0   | Memory write          |

|     |     | 1   | Passive state         |

These outputs are held to high level in the standby mode.

These are three-state output and become high impedance during hold acknowledge.

## 2.26 BUSLOCK (Bus Lock) ... For large-scale systems

The CPU uses this signal to secure the bus during the instruction immediately following the execution of the BUSLOCK prefix instruction. It is a request signal to the other master CPUs in a multiprocessor system inhibiting them from using the system bus during this time.

This output is held to high level in the standby mode, however, it is held to low level if BUSLOCK instruction is executed right before HALT instruction.

The output of this signal is three state and becomes high impedance during hold acknowledge.

2.27  $\overline{\text{RQ/AK1}}$  ,  $\overline{\text{RQ/AK0}}$  (Hold Request/ Acknowledge) ... For large-scale systems

These pins function as bus hold request inputs ( $\overline{\text{RQ}}$ ) and as bus hold acknowledge outputs ( $\overline{\text{AK}}$ ). This is the priority for these signals.

$$\overline{\text{RQ/AK1}} < \overline{\text{RQ/AK0}}$$

These pins have three-state output buffer. They also are provided with on-chip pull-up resistors. They are inactive (high level) when open.

2.28 VDD (Power Supply) ... For small- and large-scale systems

This pin is used for positive power supply.

2.29 GND (Ground) ... For small- and large-scale systems

This pin is used for the ground potential.

2.30 IC (Internally Connected)

This pin is used for tests performed at the factory by NEC. Normally, the uPD70108/70116 is used with this pin at ground potential.

## Chapter 3 Functions of Internal Block

The uPD70108/70116 consists of two independent processing unit:

a bus control unit (BCU) and an execution unit(EXU).

BCU - Prefetches instruction bytes using instruction queue

(4-byte for the uPD70108, 6-byte for the uPD70116)

EXU - Internal data processing (Execute microprogram)

### 3.1 Program Counter (PC)

The program counter is a 16-bit binary counter that stores offset data for the next programme memory address the EXU is to execute.

The PC increments each time the microprogram fetches an instruction from the instruction queue. A new location value is loaded into the PC each time a branch, call, return, or break instruction is executed. At this time, the contents of the PC are the same as the Prefetch Pointer (PFP).

### 3.2 Prefetch Pointer (PFP)

The prefetch pointer (PFP) is a 16-bit binary counter that stores the offset data for the program memory address that the bus control unit (BCU) is about to prefetch in to the instruction queue.

The PFP is incremented each time the BCU prefetches an instruction from the program memory. A new location will be loaded into the PFP whenever a branch, call, return, or break instruction is executed. At that time the contents of the PFP will be the same as those of the PC (Program Counter). The contents of PFP are an offset from the PS Program Segment) register.

### 3.3 Q0-Q3/Q0-Q5 (Prefetch Queue)

The uPD70108/70116 has 4-/6-byte instruction queue (FIFO), and it can store up to 4/6 instruction byte prefetched by the BCU. The instruction codes stored in the queue are fetched and executed by the EXU. The queue is cleared and prefetched with the instruction code of a new location when branch, call, return, or break instruction has been executed and when external interrupt has been acknowledged. Normally, the uPD70108 prefetches if the queue has one byte or more space and the uPD70116 prefetches if the queue has one word (two bytes) or more space. If the time required to prefetch the instruction code from the external memory is less than the mean

execution time of instructions which are executed sequentially, then the actual instructions cycle will be shortened by this amount of time i.e. the time needed to fetch the instruction code. This is because the instruction code to be next executed by the EXU can be available in the queue immediately after the completion of one instruction. As the result, processing speed is highly upgraded compared with the conventional CPU which fetch and execute instructions one by one. Queuing effect is lowered if there were many instructions which clears queue like the branch instruction or in the case of continuous instructions with too short instruction time.

#### 3.4 DP (Data Pointer)

This is a 16-bit register indicates read/write addresses of variables. Effective address made in the effective address generator and the register contents including memory address offsets are transferred to the DP.

#### 3.5 TEMP (Temporary Communication Register)

This is a 16-bit temporary register used by communications between external data bus and the EXU. The TEMP can be read or written by upper byte or lower byte independently for byte access. Basically, the EXU completes write operation with transferring data to the TEMP and completes read operation with recognizing the data has been transferred to the TEMP from external data bus.

#### 3.6 Segment Registers (PS,SS,DS0, and DS1)

The memory addresses accessed by the uPD70108/70116 are divided into 64K-byte logical segments. The starting (base) address of each segment is specified by a segment register, and the offset from this starting address is specified by the contents of another register or by the effective address.

These are the four types of segment registers used.

| Segment register     | Default offset        |

|----------------------|-----------------------|

| PS (Program Segment) | PFP                   |

| SS (Stack Segment)   | SP, effective address |

| DS0 (Data Segment 0) | IX, effective address |

| DS1 (Data Segment 1) | IY                    |

### 3.7 ADM (Address Modifier)

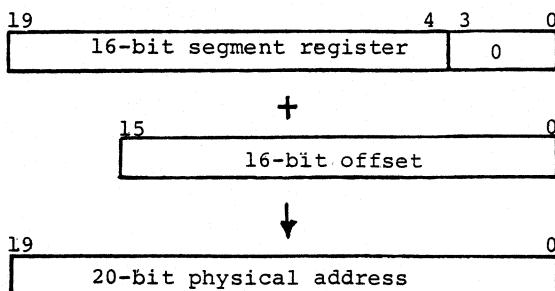

The Address Modifier performs the generation of physical address (adding segment register and PFP or DP) and increment of PFP (Prefetch Pointer).

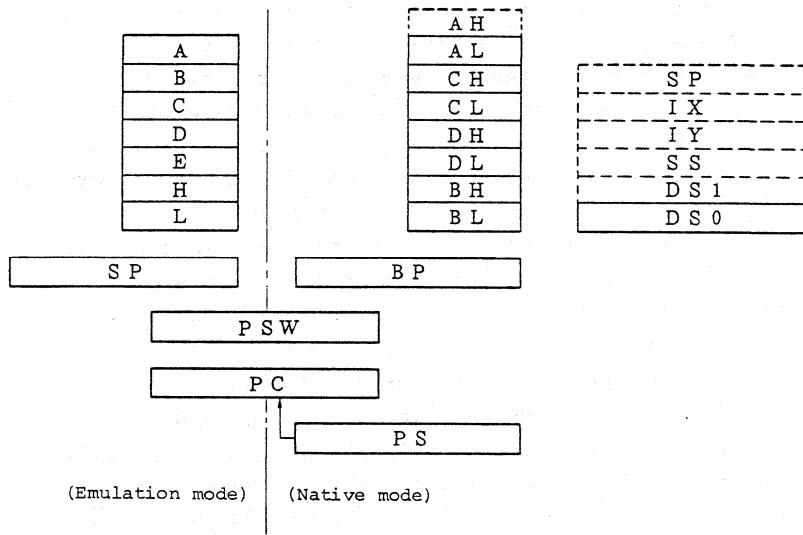

### 3.8 General-Purpose Registers (AW, BW, CW, and DW)

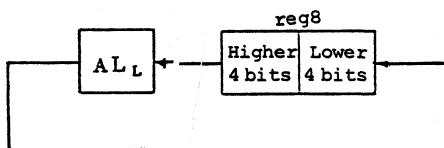

There are four 16-bit general-purpose registers. These can be accessed as 16-bit registers or as 8-bit registers by dividing them into their high and low 8-bits (AH, AL, BH, BL, CH, CL, DH, DL).

Each register is also used as a default register for processing specific instructions. These are the default assignments.

AW: Word multiplication/division, word I/O, data conversion

AL: Byte multiplication/division, byte I/O, BCD rotation, data conversion, translation

AH: Byte multiplication/division,

BW: Translation

CW: Loop control branch, repeat prefix

CL: Shift instructions, rotation instructions, BCD operations

DW: Word multiplication/division, indirect addressing I/O

### 3.9 Pointers (SP, BP) and Index Registers (IX, IY)

These registers serve as base pointers or index registers when accessing the memory using based addressing, indexed addressing, or based indexed addressing.

These registers can also be used for data transfer and arithmetic and logical operations in the same manner as the general-purpose registers. They cannot be used this way, however, as 8-bit registers.

Also, each of these registers acts as default registers for specific operations. The default assignments are:

SP: Stack operations

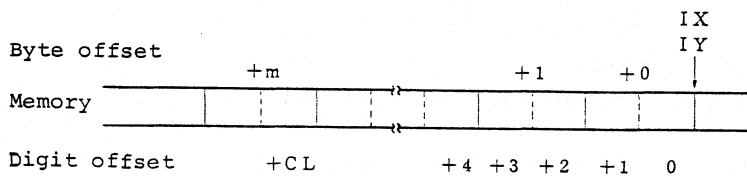

IX: Block transfer (source), BCD string operations

IY: Block transfer (destination), BCD string operations

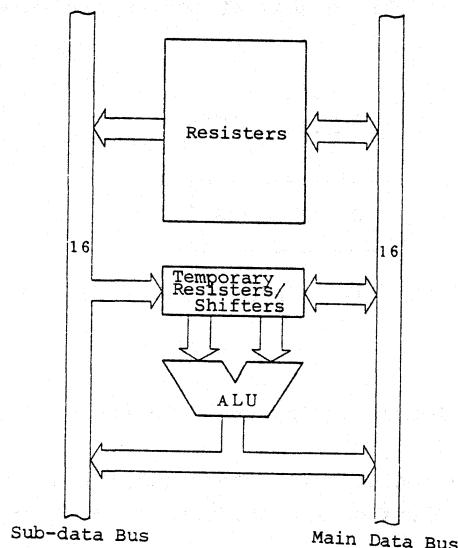

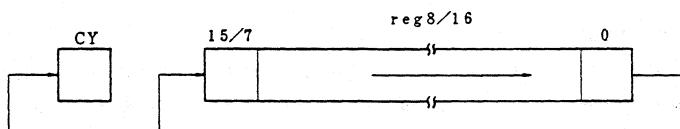

### 3.10 TA/TB (Temporary Register/Shifter A,B)

The TA/TB are 16-bit temporary register/shifter used with execution of multiply/divide and shift/rotate (including BCD rotate) instructions. When executing multiply or divide instruction TA+TB operates as a 32-bit temporary register/shifter, and TB operates as a 16-bit temporary register/shifter when executing shift/rotate instructions. Both the TA and TB can be read or written to and from the internal bus by upper byte or lower byte independently. The contents of the TA and TB are input to the ALU.

### 3.11 TC (Temporary Register C)

The TC is a 16-bit temporary register used with internal processing like the multiply or divide operation, etc. The TC content is output to the ALU.

### 3.12 ALU (Arithmetic & Logic Unit)

The Arithmetic and Logic Unit is consists of a full adder and logical operation circuit and performs these operations:

- Arithmetic operation (Add, Subtract, Multiply, Divide, increment, decrement, and complement)

- Logical operation (test, And, Or, Xor and bit test, set, clear, and complement)

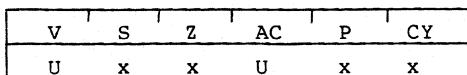

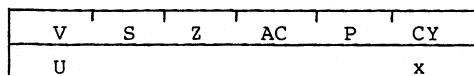

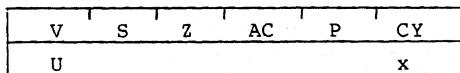

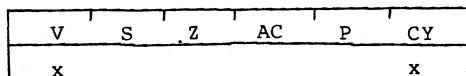

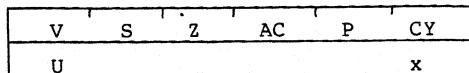

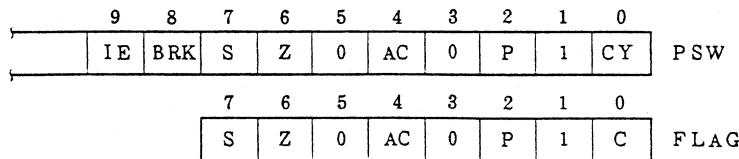

### 3.13 Program Status Word (PSW)

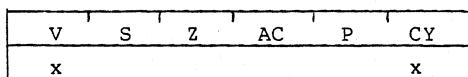

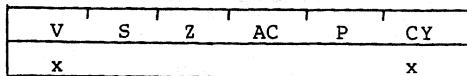

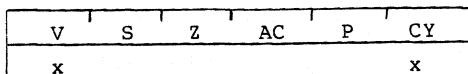

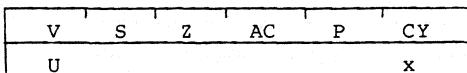

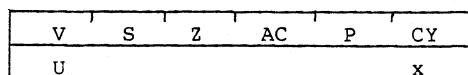

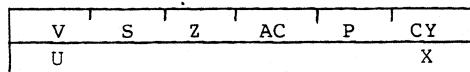

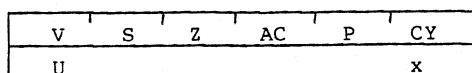

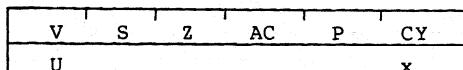

The program status word consists of the following six status and four control flags.

#### Status flags

V (Overflow)

S (Sign)

Z (Zero)

AC (Auxiliary Carry)

P (Parity)

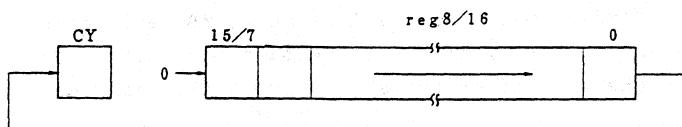

CY (Carry)

## Control Flags

MD (Mode)

DIR (Direction)

IE (Interrupt Enable)

BRK (Break)

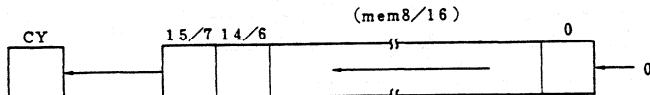

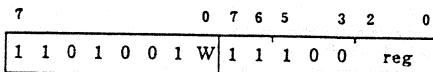

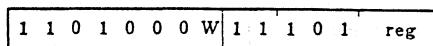

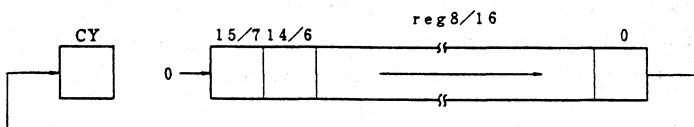

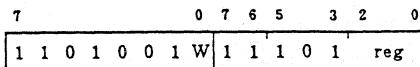

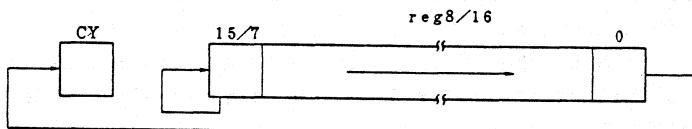

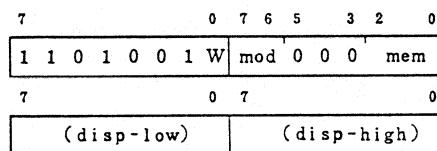

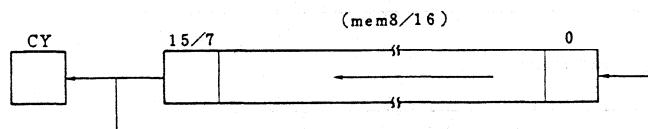

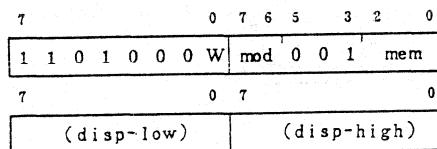

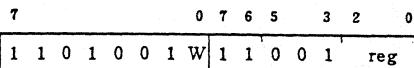

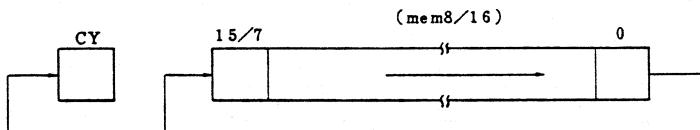

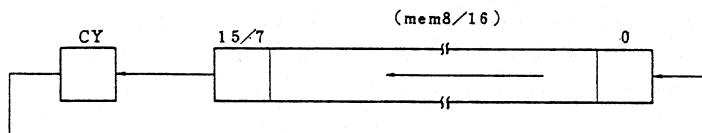

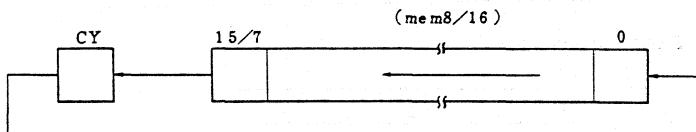

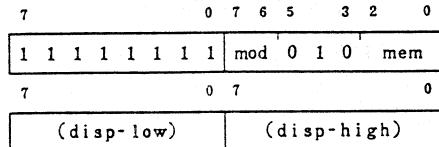

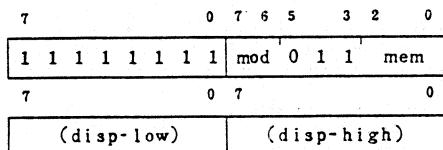

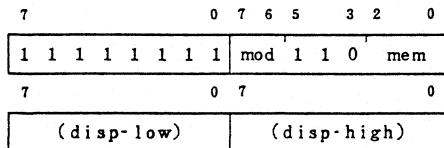

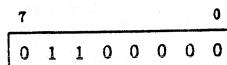

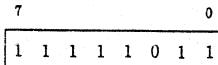

When the PSW is pushed onto the stack, the word image of the various flags is as shown here.

|    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| M  | 1  | 1  | 1  | V  | D  | I | B | S | Z | 0 | A | 0 | P | 1 | C |

| D  |    |    |    |    | I  | E | R |   |   |   | C |   |   |   | P |

The status flags are set and reset depending on the result (data value) of each type of instruction executed.

Instructions are provided to set, reset, and not (or complement) the CY flag directly.

Other instructions set and reset the control flags and control the operation of the CPU.

## 3.14 LC (Loop Counter)

The Loop Counter (LC) is a 16-bit register which counts these items.

- Loop number of the primitive block transfer and input/output instructions (MOVBK, OUTM, etc.) controlled with repeat prefix instructions (REP, REPC, etc.).

- Shift number of the multi-bit shift/rotate instructions.

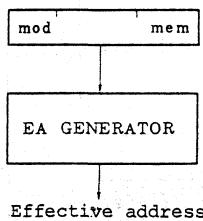

### 3.15 EAG (Effective Address Generator)

The Effective Address Generator (EAG) performs high-speed effective address calculation necessary for memory access. This completes all the calculations with 2 clocks for every addressing mode.

This fetches the instruction byte (2nd or 3rd byte) which has operand specifying field, if the instruction needs memory access. Then calculates effective address and transfers it to the DP (Data Pointer) and generates control signals relating to handling ALU and corresponding registers. In addition, if it's necessary, the EAG requests to the BCU for starting the bus cycle (memory read).

### 3.16 Instruction Decoder

The Instruction Decoder classifies 1st byte of an instruction code into some groups with specific function and holds them during macro-instruction execution.

### 3.17 Microaddress Register

The microaddress register specifies address of an microinstruction ROM to be next executed. At starting of an microinstruction execution, the 1st byte of an instruction byte(s) stored in the queue is fetched in this register and it specifies a start address of the corresponding microinstruction sequence.

### 3.18 Microinstruction ROM

The Microinstruction ROM has 1024 words by 29 bits of microinstructions.

### 3.19 Microinstruction Sequencer

The Microinstruction Sequencer controls the microaddress register operation, microinstruction ROM output, and synchronizing the EXU with BCU.

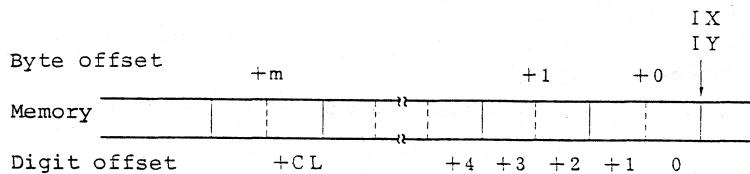

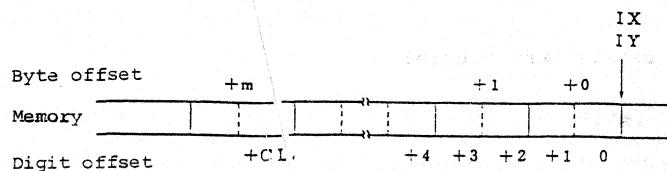

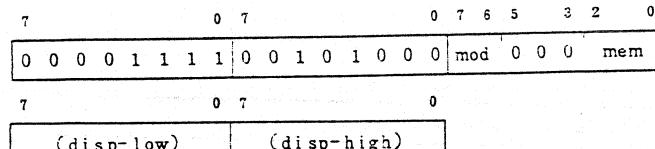

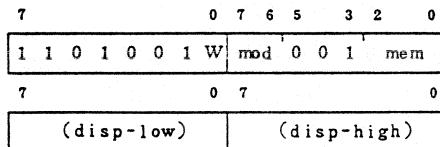

#### 4.1 Memory Configuration and Accessing

The  $\mu$ PD70108/70116 can access and address up to 1M bytes (512K words) of memory area. The memory area is addressed by the address information output by the 20-bit address bus (A19 to A0).

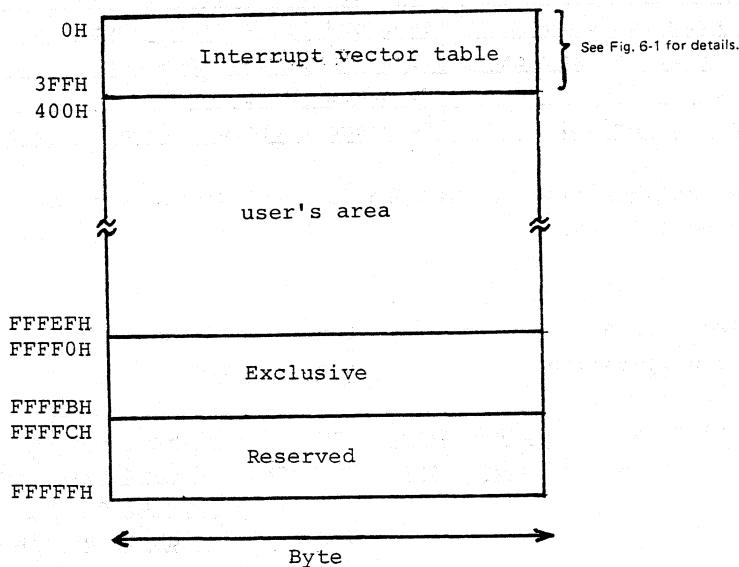

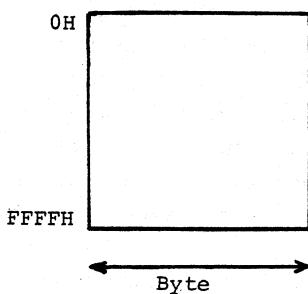

The memory map is shown in Fig. 4-1.

The 1K bytes from addresses 0H to 3FFH are allocated as an interrupt vector table. This area may be used for other purposes in some systems. The 12 bytes from address FFFF0H to FFFF0H are automatically used by the CPU when it is started or reset and therefore cannot be used for any other purpose. The four bytes from addresses FFFFCH to FFFFFH are reserved for future use and consequently not available to the user.

Fig. 4-1 Memory Map

The memory stores such things as instruction codes, interrupt start addresses, stack data, and general variables. Some of these are stored in byte units and the others are in word units.

These data can be stored in both even ( $A0=0$ ) and odd ( $A0=1$ ) addresses generated by an instruction. The area where interrupt start addresses (interrupt vector table) are stored is addressed only by using even addresses, however. The  $\mu$ PD70116 is so designed that a word data can be accessed regardless of whether the word data is of an even or an odd address, allowing both the even and odd addresses to be generated by an instruction.

Table 4-1 shows the address and data configuration of each data.

Table 4-1

| Data                   | Address  | Data configuration    |

|------------------------|----------|-----------------------|

| Instruction code       | Even/odd | 1/2/3/4/5/6 bytes     |

| Interrupt vector table | Even     | 2 words/vector        |

| Stack                  | Even/odd | Word                  |

| General variable       | Even/odd | Byte/word/double word |

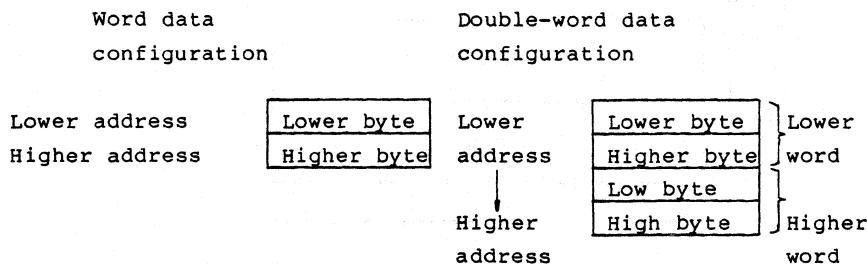

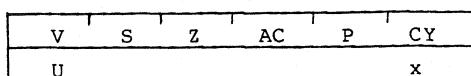

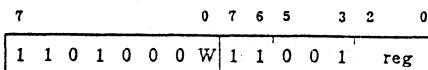

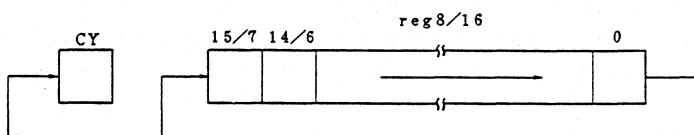

The configuration of the word data and double-word data are as follows:

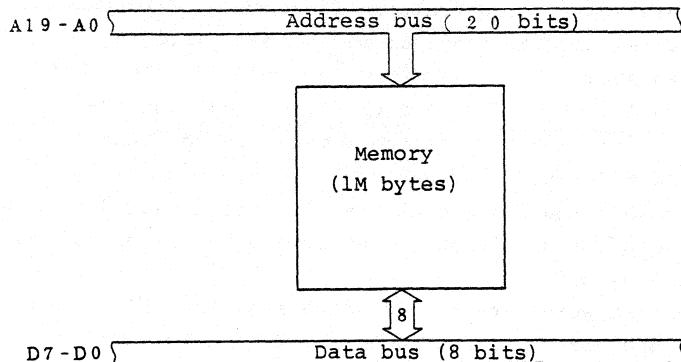

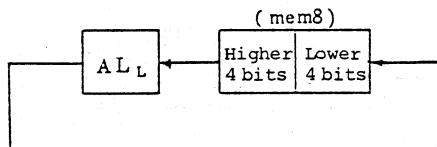

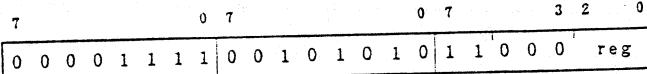

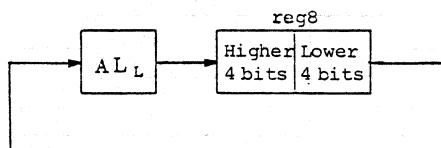

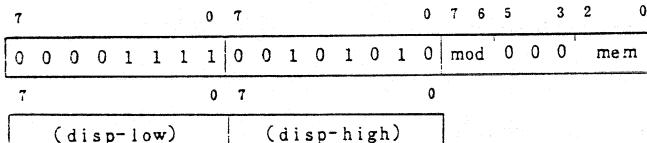

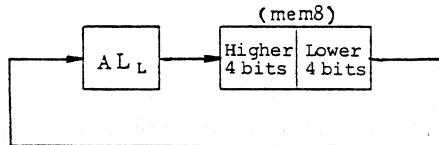

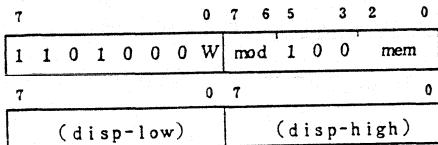

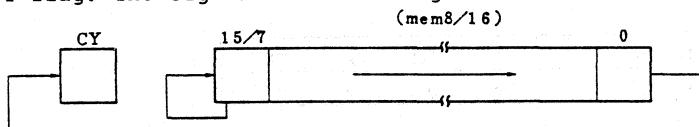

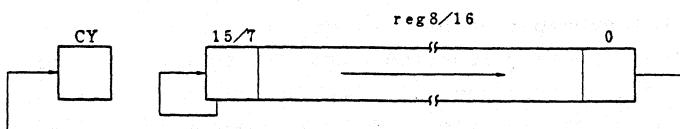

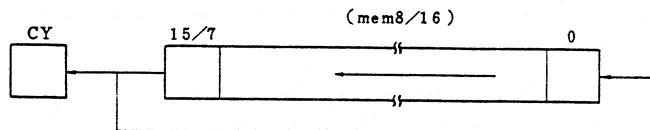

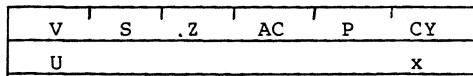

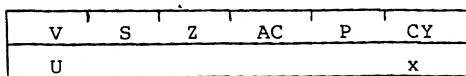

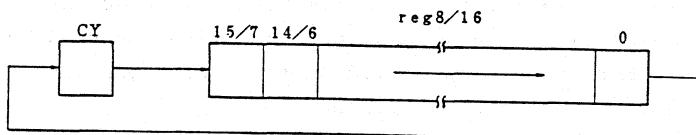

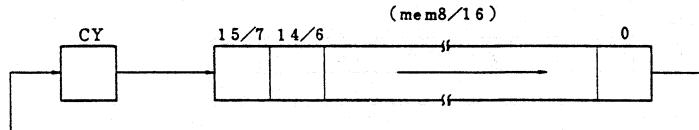

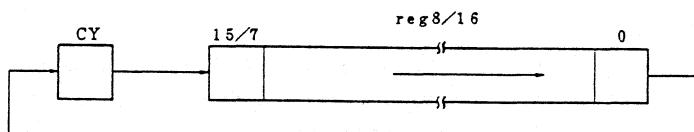

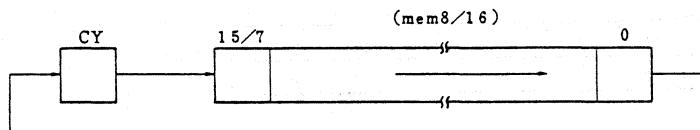

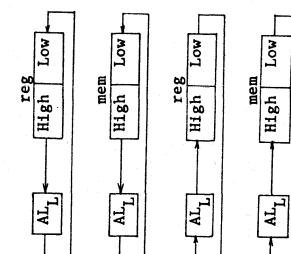

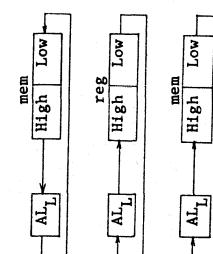

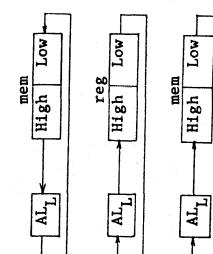

The interface between the memory and the CPU  $\mu$ PD70108 is shown in Fig. 4-2. The interface between the memory and the CPU  $\mu$ PD70116 is shown in Fig. 4-3.

Fig. 4-2 Interface Between Memory and  $\mu$ PD70108

Because the data bus of the  $\mu$ PD70108 is 8 bits wide, a byte data is accessed during one bus cycle and two bus cycles are required to access word data regardless of whether the word data is of an even or odd address.

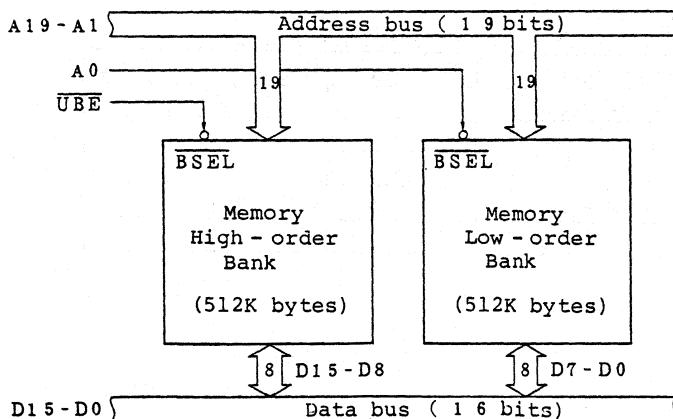

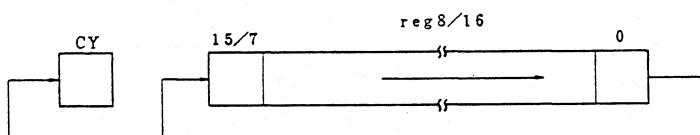

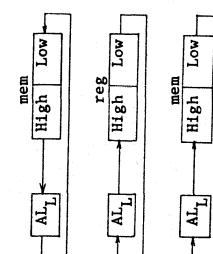

Fig. 4-3 Interface Between Memory and  $\mu$ PD70116

Because the data bus of the  $\mu$ PD70116 is 16 bits wide, in principle the  $\mu$ PD70116 has the capability to transfer a 16-bit word data within one bus cycle. This is true, however, only when an even-address word data (i.e., when  $A0=0$ ) generated by an instruction is accessed. Two bus cycles are required to transfer odd-address word data (i.e., when  $A0=1$ ).

The  $A0$  signal in Fig. 4-3 is active low, enabling the byte data in the low bank of the memory. In addition to the address information output from the address bus, a  $\overline{UBE}$  (Upper Byte Enable) signal that is also active low is output. The  $\overline{UBE}$  signal enables the byte data in the higher bank of the memory.

When accessing word data of odd addresses, the  $\overline{UBE}$  signal becomes 0 and the  $A0$  signal becomes 1 during the first bus cycle. Only the higher byte of an address is accessed at this time. Subsequently, the  $\overline{UBE}$  signal automatically becomes 1 and the lower 16 bits of the address information ( $A15-A0$ ) is incremented by one, in other words, the  $A0$  signal becomes 0. Then the lower byte of the address is accessed.

The word data of an even address is accessed during one bus cycle when the  $\overline{UBE}$  and  $A0$  signals are 0s.

Table 4-2 summarizes the above description.

Table 4-2  $\mu$ PD70116 Data Access

| Accessed data       | $\overline{UBE}$ | $A0$ | No. of bus cycles |

|---------------------|------------------|------|-------------------|

| Word (even address) | 0                | 0    | 1                 |

| Word (odd address)  | 0                | 1    | 2                 |

|                     | 1                | 0    |                   |

| Byte (even address) | 1                | 0    | 1                 |

| Byte (odd address)  | 0                | 1    | 1                 |

The  $\mu$ PD70116 normally accesses (prefetches) instruction codes in word units. If a branch operation to an odd address takes place, however, only one byte is fetched from that odd address. After that, instruction codes are prefetched in word units again.

When the interrupt vector table is accessed in response to an interrupt, even addresses are always generated from vector numbers (0 to 255) as the addresses of the vector table. Data of even addresses are always accessed as word data when the interrupt vector table is accessed.

Consequently, when the vector table is accessed in response to an interrupt, two bus cycles are required because two words (segment base and offset) are accessed. One bus cycle to access the memory requires four clocks. As a result, each time word data from an odd address is accessed, four additional clocks of instruction execution time are necessary compared to that required when accessing an even-address word data. This only applies to instructions that require more than one bus cycle.

When transferring a word data from one memory area to another, the memory must be accessed twice because the word data must be read from the source first and then written to the destination. If both the source and the destination are odd addresses the execution time will be maximized.

The same holds true during a stack operation. The contents of a register are automatically saved to the stack when an interrupt is serviced. These contents are all word data. If they are processed by using an odd address, therefore, the number of bus cycles required is twice as many as the bus cycles required to process using an even address.

The result is a delay in the interrupt response time. Consideration should be given to this point.

As is apparent from this discussion, it's a good idea to allocate even addresses to word data that can be checked by the program when accessed in the  $\mu$ PD70116.

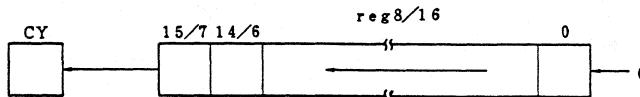

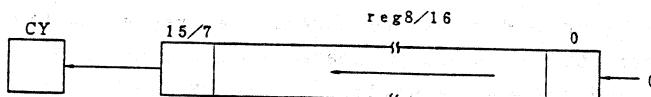

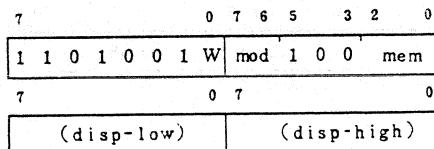

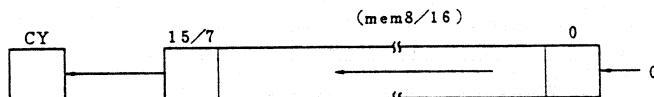

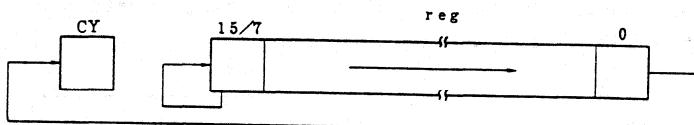

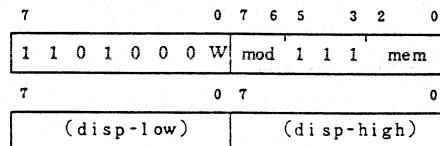

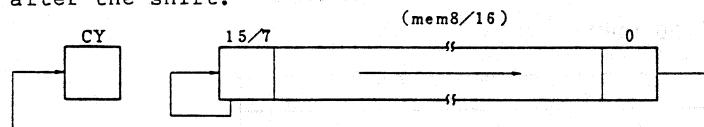

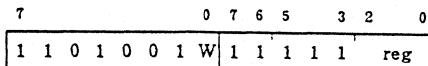

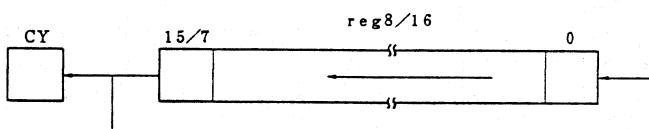

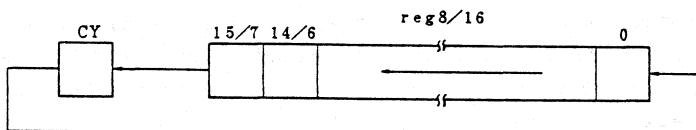

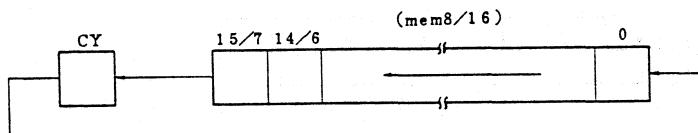

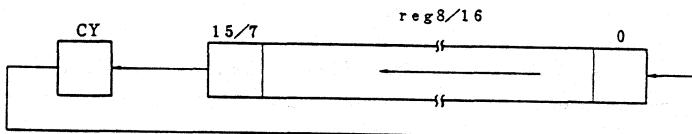

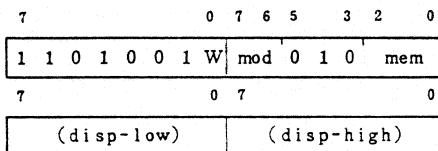

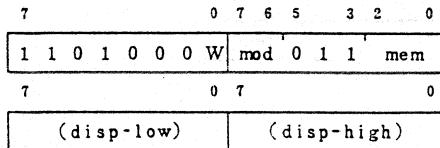

**Example:** Execution time of MOV reg,mem instruction (number of clocks for word data accessed one time)

Byte data 11:  $\mu$ PD70108/70116

Word data 15:  $\mu$ PD70108/odd address of 70116

11: even address of  $\mu$ PD70116

#### 4.2 I/O Configuration and Accessing

The  $\mu$ PD70108/70116 can access up to 64K bytes (32K words) of I/O address area used independently of the memory.

The I/O address area is addressed by address information output by the lower 16/8 bits of the address bus.

The I/O map is shown in Fig. 4-4.

Fig. 4-4 I/O Map

Unlike the memory, the segment method is not applied to the I/O address area.

When I/O addresses are output, 0s are output to the higher four bits (A19 to A16) of the address bus.

Since data are transferred between the CPU and the I/O address area in byte or word units, both 8-bit and 16-bit I/O devices can be connected to the  $\mu$ PD70116 and only 8-bit I/O devices can be connected to the  $\mu$ PD70108.

However, in the  $\mu$ PD70116, a word data of an even address, in the same way as when accessing the memory, requires only one bus cycle and two cycles are required to access odd-address word data.

When the  $\mu$ PD70116 accesses an 8-bit I/O device, bit A0 of the I/O address information is only used to select an I/O device. The A1 and higher bits are used to select a device and several registers in that device.

Consequently, only even addresses should be assigned to an I/O device as well as to the internal registers of the I/O devices so that the registers can be selected using only even addresses. Similarly, I/O devices whose internal registers are assigned with odd addresses must be assigned with an odd address. If memory-mapped I/O configuration (allocating a certain area of the memory to an I/O address area) is employed, the I/O address area can be allocated to a 1M-byte memory area. In this way, numerous addressing modes of the memory and operation processes can be directly performed on I/O devices.

For example, if a bit operation instruction for the memory is used, one line of a specific I/O port can be tested (to examine 1 or 0), set (to 1), cleared (to 0), or inverted.

In a memory-mapped I/O configuration, however, control signals output from the CPU are regarded as those for the memory. The I/O device is therefore distinguished from the memory only by address information. For this reason, then, be careful that addresses of variables or the stack do not conflict with the addresses allocated to I/O.

## Chapter 5 Read/Write Timing of Memory and Input/Output

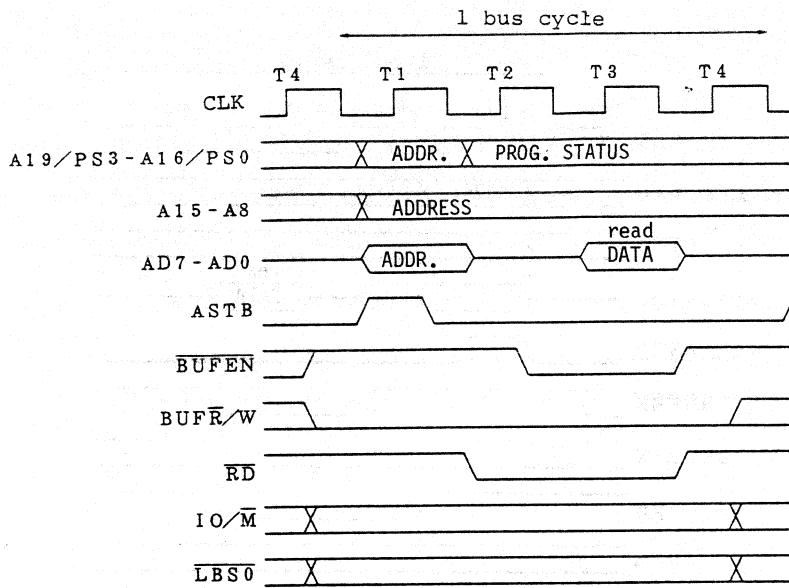

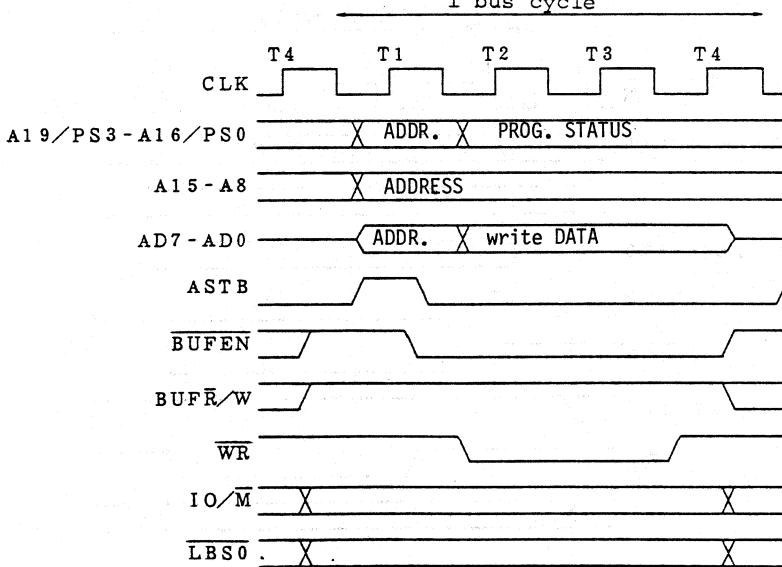

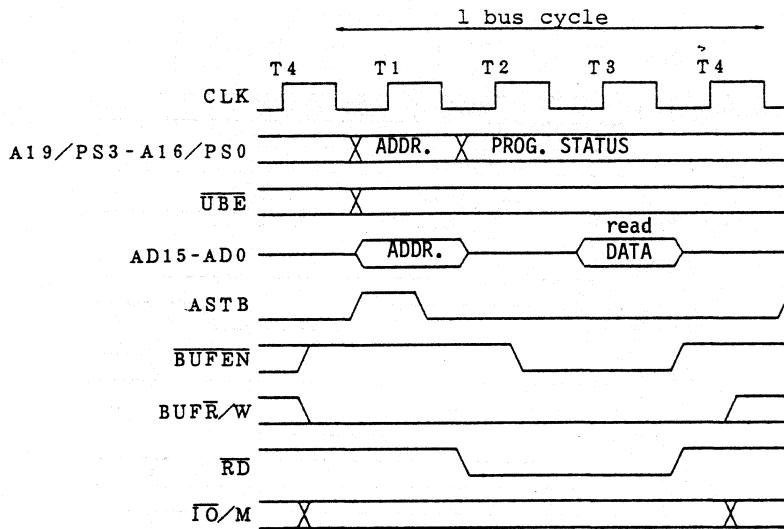

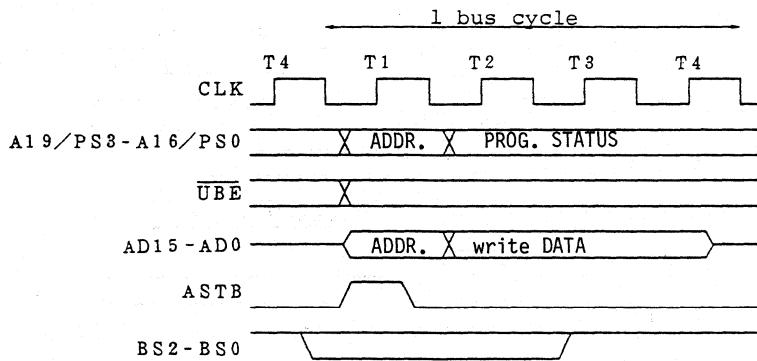

Read/write timings of the  $\mu$ PD70108/70116 memory and I/O are shown in Figs. 5-1 to 5-8. One bus cycle is required for each access (read/write) of the memory or I/O address area. A bus cycle is basically made up of four states (clocks): T1 to T4. One state is 200ns when the microprocessor operates at 5MHz.

The  $\mu$ PD70108 and  $\mu$ PD70116 fetch an instruction code and read data using exactly the same timing (see Figs. 5-1, 5-3, 5-5, and 5-7). If a particular instruction calls for a longer internal process time, the EXU fetches the instruction code of that instruction from the instruction queue and executes it. After that, the BCU continues prefetching instructions to the instruction queue until the queue becomes full. Should the EXU not fetch an instruction code from the instruction queue because another instruction is being executed, the BCU will not prefetch the next instruction. Instead, it automatically inserts an idle state (TI) after state T3. More idle states are inserted until the EXU finishes executing the instruction being processed. Then it fetches the next instruction code from the instruction queue.

When the next instruction code is fetched, the BCU advances the state of the bus cycle from state T4 to T1. For a memory or I/O device whose access time is slow, the BCU detects a READY signal sent from the memory or the I/O device. If the READY signal is at low level, BCU will not advance the bus cycle state from T3 to T4. Instead, it will delay by inserting a wait state (TW). When the READY signal becomes high, execution advances the bus cycle state from T4 to T1 so the next instruction can be fetched.

When the wait state TW is inserted, the current level of each signal is retained and the read/write timing is expanded.

Fig. 5-1 Read Timing of  $\mu$ PD70108 Memory and I/O

(for small-scale systems)

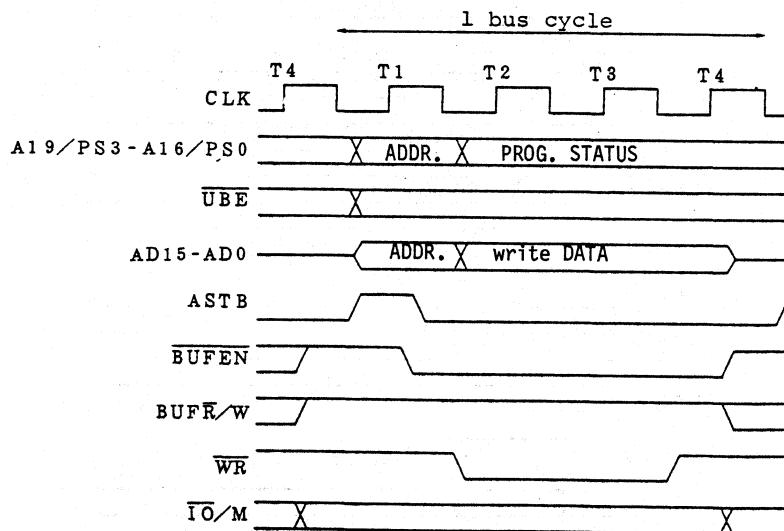

Fig. 5-2 Write Timing of  $\mu$ PD70108 Memory and I/O

(for small-scale systems)

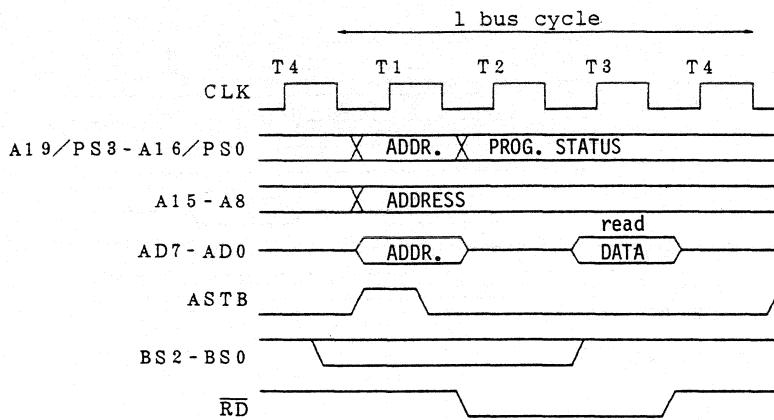

Fig. 5-3 Read Timing for  $\mu$ PD70116 Memory and I/O

(for small-scale systems)

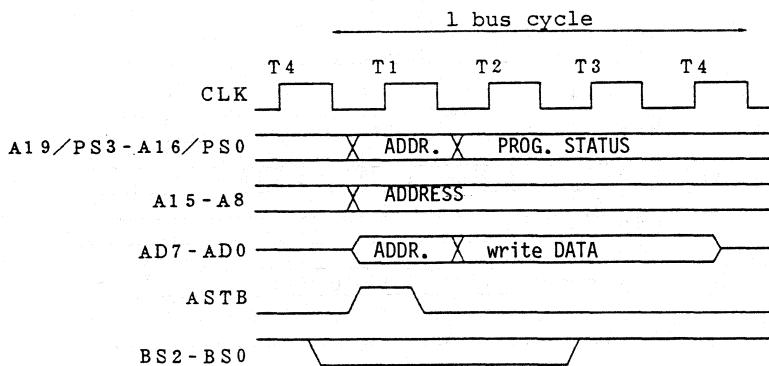

Fig. 5-4 Write Timing for  $\mu$ PD70116 Memory and I/O

(for small-scale systems)

Fig. 5-5 Read Timing for  $\mu$ PD70108 Memory and I/O

(for large-scale systems)

Fig. 5-6 Write Timing for  $\mu$ PD70108 Memory and I/O

(for large-scale systems)

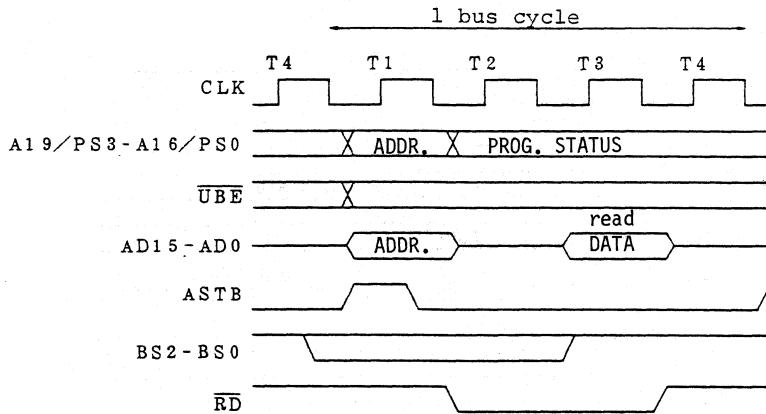

Fig. 5-7 Read Timing for  $\mu$ PD70116 Memory and I/O

(for large-scale systems)

Fig. 5-8 Read Timing for  $\mu$ PD70116 Memory and I/O

(for large-scale systems)

## Chapter 6 Interrupts

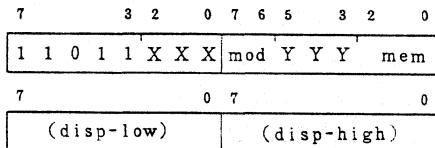

These interrupts accepted by the  $\mu$ PD70108/70116 are roughly classified into two types. One type is caused by an external interrupt request and the other is caused by a software process. Both types are vectored interrupts.

When an interrupt occurs, therefore, a location in the interrupt vector table that has been prepared beforehand is selected either automatically (a fixed vector) or by specification (a variable vector). This selected location determines the start address of the corresponding interrupt routine.

Table 6-1 shows the vector, priority, and number of clocks required to process each interrupt.

Table 6-1 Interrupt Source

|          | Interrupt source         | No. of clocks | Vector | Priority |

|----------|--------------------------|---------------|--------|----------|

| External | NMI (rising-edge active) | 58/38         | 2      | 2        |

|          | INT (high-level active)  | 68/49         | 32-255 | 3        |

| Software | DIVU divide error        | 65/45         |        |          |

|          | DIV divide error         | 65-75/45-55   | 0      |          |

|          | CHKIND boundary over     | 81-84/53-56   | 5      | 1        |

|          | BRKV                     | 60/40         | 4      |          |

|          | BRK3                     |               | 3      |          |

|          | BRK imm8                 | 58/38         | 32-255 |          |

|          | BRKEM imm8               |               |        |          |

|          | CALLN imm8               |               |        |          |

|          | BRK flag (single step)   |               | 1      | 4        |

NOTE: The number of clocks to the left of the slash (/) is for the  $\mu$ PD70108 and the number on the right is for the  $\mu$ PD70116.

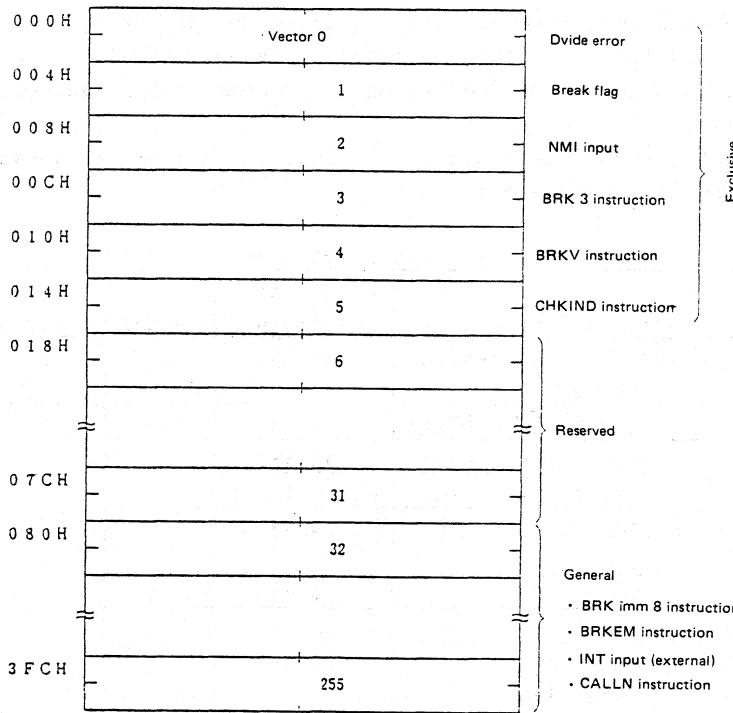

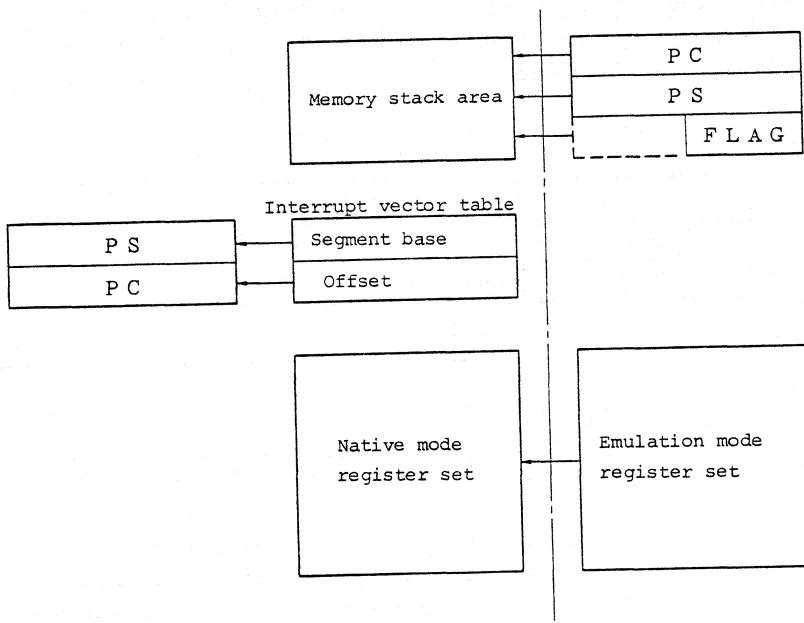

The interrupt vector table is shown in Fig. 6-1. This table is allocated to a 1K-byte memory area (from addresses 000H to 3FFH) and can hold up to 256 vectors (four bytes are required per vector).

Fig. 6-1 Interrupt Vector Table

The interrupt sources that can use vectors 0 to 5 are specified and vectors 6 to 31 are reserved. These vectors, therefore, are not for general use. Vectors 32 to 255 are for general use. These vectors are used for four interrupt sources: a 2-byte break, BRKEM, CALLN instructions (during emulation), and INT input.

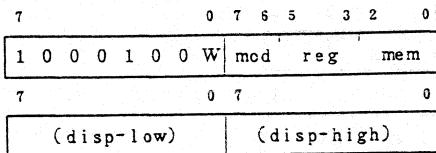

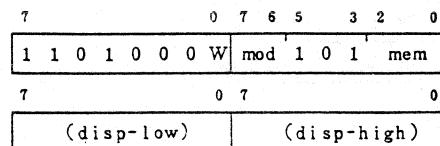

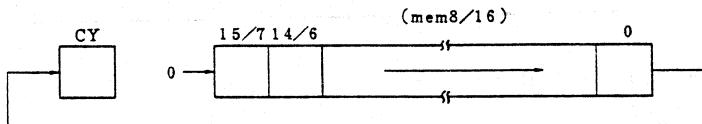

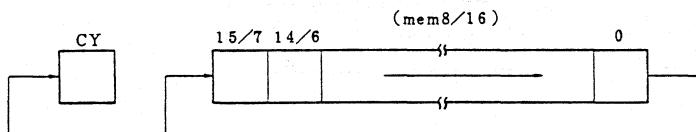

Four bytes are used for each interrupt vector. The two bytes of the lower address and the two bytes of the higher address are loaded to the programmable counter (PC) as an offset and a base, respectively.

Example: vector 0

|         |         |

|---------|---------|

| 0 0 0 H | 0 0 1 H |

| 0 0 2 H | 0 0 3 H |

PS - (0 0 3 H, 0 0 2 H)

PC - (0 0 1 H, 0 0 0 H)

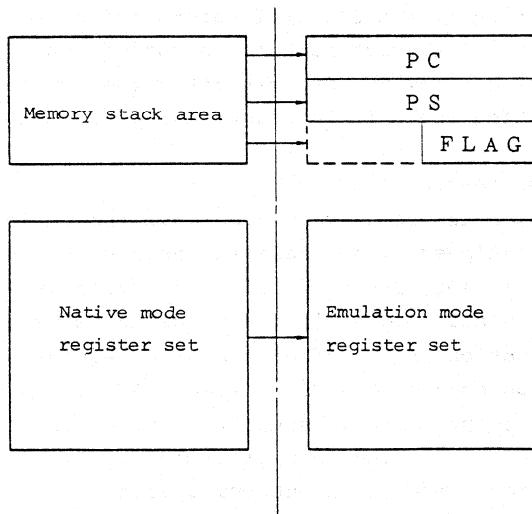

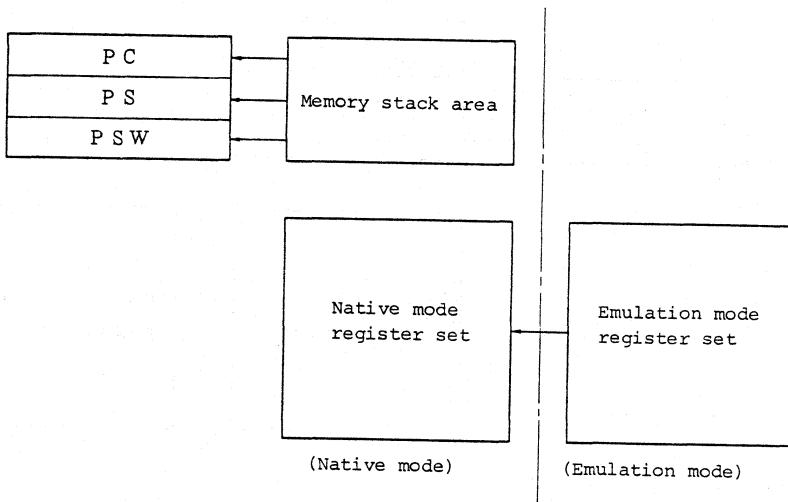

Based on this format, the contents of each vector are initialized at the beginning of a program. The basic steps to be followed when the program execution jumps to an interrupt routine are as follows:

(SP-1, SP-2)  $\leftarrow$  PSW

(SP-3, SP-4)  $\leftarrow$  PS

(SP-5, SP-6)  $\leftarrow$  PC

SP  $\leftarrow$  SP-6

IE  $\leftarrow$  0, BRK  $\leftarrow$  0, MD  $\leftarrow$  1

PS  $\leftarrow$  higher vector

PC  $\leftarrow$  lower vector

Because the interrupt enable (IE) and break (BRK) flags are reset when an interrupt routine is started, maskable interrupts (INT) and single-step interrupts are disabled.

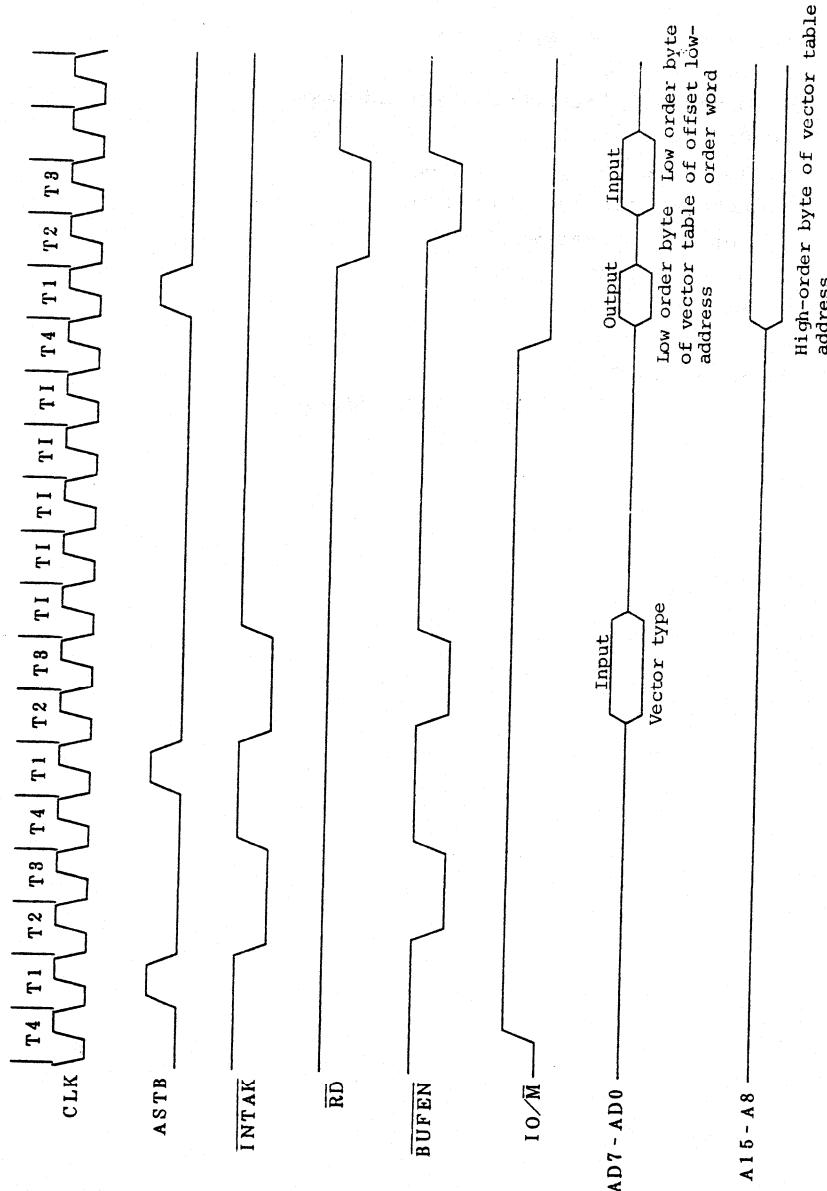

#### 6.1 INT Interrupts

If an INT input signal is detected at high level at the end of executing one instruction while interrupt is enabled (IE=1), the INT interrupt request will be acknowledged unless the NMI and hold request signals are active at the same time. The program execution then enters an interrupt acknowledge cycle (see Figs. 6-2 and 6-3).

The interrupt acknowledge cycle consists of two bus cycles. The INTAK, ASTB, and BUFEN signals are output during the first cycle. Although the bus cycle is started, initially no data read/write operation is performed and the address/data bus becomes high impedance. At this time the hold request signal is not accepted. If the  $\mu$ PD70108/70116 is in the maximum mode, the BUSLOCK signal is output, inhibiting other devices from using the bus.

The first interrupt acknowledge cycle is necessary to synchronize with the external interrupt controller. When the INTAK, ASTB, and BUFEN signals are output during the second interrupt acknowledge cycle, the external interrupt controller sends an interrupt vector to the data bus (AD7 to AD0).

After the second interrupt acknowledge cycle has been completed, the location in the interrupt vector table corresponding to the vector obtained during that acknowledge cycle is accessed. (At the same time, the contents of the PSW, PS, and PC are saved.) The interrupt start address is then output according to the contents of the interrupt vector table and the interrupt process routine is started.

The following provides interrupt acknowledge operations performed by the  $\mu$ PD70108 and  $\mu$ PD70116.

- °  $\mu$ PD70108 interrupt acknowledge operation

- 1. Acknowledge cycle (first)

- 2. Acknowledge cycle (second)

- 3. Read lower byte of offset word

- 4. Read higher byte of offset word

- 5. Read lower byte of segment word

- 6. Read higher byte of segment word

- 7. Save lower byte of PSW

- 8. Save higher byte of PSW

- 9. Save lower byte of PS

- 10. Save higher byte of PS

11. Save lower byte of PC

12. Save higher byte of PC

13. Output interrupt start address.

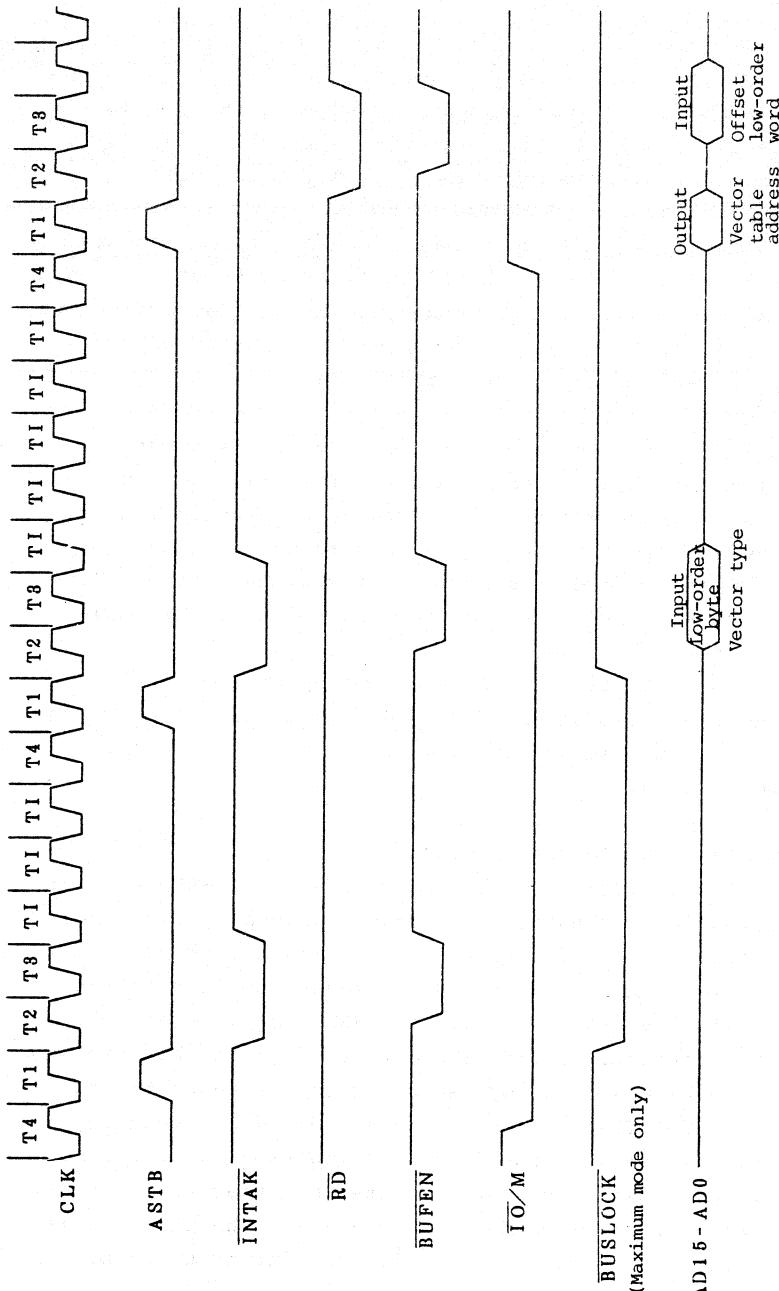

- μPD70116 interrupt acknowledge cycle

1. Acknowledge cycle (first)

2. Acknowledge cycle (second)

3. Read offset word

4. Read segment word

5. Save PSW

6. Save PS

7. Save PC

8. Output interrupt start address

Fig. 6-2 Interrupt Acknowledge Timing ( $\mu$ PD70108)

Fig. 6-3 Interrupt Acknowledge Timing ( $\mu$ PD70116)

During the first interrupt acknowledge cycle, no idle state (TI) is inserted in the bus cycle of the  $\mu$ PD70108. In the  $\mu$ PD70116, however, three TI's are inserted. During the second interrupt acknowledge cycle, five TI's are inserted in the bus cycles of both microprocessors. The CPU's of both the  $\mu$ PD70108 and  $\mu$ PD70116 read an 8-bit vector during the second interrupt acknowledge cycle. The number of cycles required to save the contents of the PSW, PS, and PC are different for the two microprocessors.

This is because the width of the  $\mu$ PD70108 data bus is smaller than that of the  $\mu$ PD70116. That is, two bus cycles are required for the  $\mu$ PD70108 to perform each of the necessary operations such as reading an offset word and a segment word, and saving the PSW, PS, and PC. In contrast, the  $\mu$ PD70116 performs each of these operations within one bus cycle.

The UBE signal of the  $\mu$ PD70116 remains at low level during the first and second interrupt acknowledge cycles and during the subsequent access of the offset and segment words.

## 6.2 BRK Flag (Single-Step) Interrupt

The  $\mu$ PD70108/70116 is provided with a single-step interrupt function that is useful for program debugging and other operations. This interrupt is controlled by the break (BRK) flag; bit 8 of the PSW. However, no instruction that directly sets or resets the BRK flag is available and the contents of the PSW must be saved to the stack to control the BRK flag. By restoring the contents to the PSW, the BRK flag is indirectly set or reset. When the BRK flag is set, an interrupt routine (monitor program, etc.) specified by vector 1 is started after the following instruction has been executed. The BRK flag is reset at this point together with the interrupt enable (IE) flag.

While the interrupt routine is being executed, the number of single-steps is checked. If it is judged that the single-step operation may be terminated, a memory operation instruction resets the BRK flag that is now saved in the stack. The CPU operation then returns to the main routine after which the next sequence of instructions is successively carried out.

If the execution returns to the main routine without operation of the BRK flag, the BRK (=1) flag saved to the stack will be restored to the PSW. One instruction of the main routine is then executed and vector 1 interrupt is caused again.

### 6.3 Timing That Does Not Accept Interrupts

While an instruction that directly sets data in the segment register is being executed or while the program execution is between three types of prefix instructions and the next single instruction or between the EI instruction and the next instruction, neither NMI, INT interrupts, nor single-step break is acknowledged as shown below.

- ° Between one of these instructions and the next instruction--

MOV sreg, reg16; Mov sreg,mem16;

MCV reg16, sreg; MOV mem16,sreg; POP sreg

- ° Between one of these instructions and the next instruction--

segment override prefix (PS:, SS:, DS0:, DS:)

- ° Between one of these instructions and the next instruction--

repeat prefix (REPC, REPNC, REP, REPE, REPZ, REPNE,

REPNZ)

- ° Between this instruction and the next instruction--

bus lock prefix (BUSLOCK)

- ° Between the EI instruction and the next instruction

An NMI request signal generated during the abovementioned interrupt disable timing will be internally retained and acknowledged on completion of the subsequent single instruction.

#### 6.4 Interrupt process During Block Transfer Instruction Execution

Should an external interrupt (NMI or INT when the interrupt is enabled) occur while a primitive block transfer/comparison, or I/O instruction is being executed, the CPU will acknowledge the interrupt and branches the execution to the corresponding interrupt address. At the beginning of the interrupt routine started in this manner, the contents of CW register that has been serving as a counter for block data will be saved to the stack. After the contents of the CW have been restored at the end of the interrupt process routine, the execution of the CPU will be returned to the original routine. In this way, the interrupted block operation will be resumed.

If prefix instructions have existed before the block operation instruction, up to three instructions will be retained.

On returning from the interrupt routine, the execution must return to the address at which the prefix instruction is held. For this purpose, the uPD70108/70116 is so designed that the return address when it is saved (minus one address per prefix instruction) is modified.

To make the best use of these functions, more than three prefix instructions must not be placed before a block operation instruction.

[Example of correct procedure]

```

BUSLOCK

REPC

NMI --> CMPBKB dst-block, SS: src-block

```

In this example, the BUSLOCK, REPC, and SS: instructions are executed when the program execution has been returned from the NMI interrupt process.

[Example of incorrect procedure]

```

BUSLOCK

REP

REPC

NMI + CMPBK dst-block, SS: src-block

```

In this example, it is judged that two types of prefix instructions exist (repeat prefix instruction is the same type) and two return addresses are accordingly modified. In reality, however, the prefix instruction occupies 3 addresses. Consequently, the program execution cannot return from the interrupt routine to the BUSLOCK instruction and, instead, will return to the REP instruction.

## Chapter 7 Standby Function

The  $\mu$ PD70108/70116 is provided with standby mode. In standby mode, program execution can be terminated or resumed as required retaining all the statuses in the CPU. Moreover, by making the most of the CMOS characteristics of the microprocessor, the clock is not supplied except to the circuits related to the hold and standby release functions. As a result, the power consumption can be reduced to approximately 1/10 of that required for normal operation in native or emulation mode.

### 7.1 Setting Standby Mode

The standby mode can be set by executing the HALT instruction in native mode. When the microprocessor is in emulation mode, execute the HLT instruction to set the standby (hold) mode.

### 7.2 Standby Mode

In standby mode, the clock is not supplied to any circuit except those required to release the standby mode and those related to the hold function. Even if the supply of the clock is stopped, however, all CPU statuses immediately before the standby mode are retained.

By stopping the supply of the clock to most of the circuits, power consumption drops to approximately 1/10th that normally required to execute programs.

Although the bus hold function can be used in standby mode, the CPU reenters the standby mode when the hold acknowledge cycle is completed.

The status of each output signal in standby mode is as follows:

Table 7-1 Signal Status in the Standby Mode

|                         | Output signal             | Status                                                                                                  |

|-------------------------|---------------------------|---------------------------------------------------------------------------------------------------------|

| Large-scale system mode | OS1,0                     | Fixed at low level                                                                                      |

|                         | BS2-BS0                   | Fixed at high level                                                                                     |

|                         | BUSLOCK                   | Fixed at high level (however fixed at low level if BUSLOCK instruction exists before HALT instruction.) |

| Small-scale system mode | INTAK                     |                                                                                                         |

|                         | BUFEN                     | Fixed at high level                                                                                     |

|                         | WR                        |                                                                                                         |

|                         | RD                        |                                                                                                         |

|                         | ASTB                      | Fixed at low level                                                                                      |

|                         | BUFR/W                    |                                                                                                         |

|                         | IO/M ( $\mu$ PD70108)     | Fixed at either high or low level                                                                       |

|                         | IO/M ( $\mu$ PD70116)     |                                                                                                         |

|                         | LBS0 ( $\mu$ PD70108)     |                                                                                                         |

|                         | UBE ( $\mu$ PD70116)      | Fixed at high level                                                                                     |

| Common                  | A19/PS3-A16/PS0           |                                                                                                         |

|                         | A15-A8 ( $\mu$ PD70108)   | Fixed at either high or low level                                                                       |

|                         | AD7-AD0 ( $\mu$ PD70108)  |                                                                                                         |

|                         | AD15-AD0 ( $\mu$ PD70116) |                                                                                                         |

As can be seen from this table, the control outputs provided with an active level are fixed at inactive level in standby mode. The other output signals are fixed at either high or low level.

The standby mode is released by input of the RESET signal or an external interrupt (NMI or INT).

### 7.3 Releasing Standby Mode by External Interrupt Input

The standby mode is released when an input NMI or INT signal becomes active. If the standby mode has been released by the INT signal, the operation the CPU performs is determined depending on whether the interrupt has been enabled (EI) or disabled (DI) when the INT signal is recognized.

#### 7.3.1 Releasing Standby Mode by NMI Input

Regardless of whether the CPU enters the standby mode from the native mode or the emulation mode, the standby mode is unconditionally released and the NMI interrupt routine of the native mode is started. If the RETI instruction is executed at the end of the NMI servicing routine, the CPU can reenter the mode set before the CPU entered the standby mode. The program execution is then resumed starting from the instruction next to the HALT/HLT instruction.

#### 7.3.2 Releasing Standby Mode by INT input

##### (1) When interrupt is disabled (DI)

When the standby mode has been released, the CPU enters the mode that had been set before the standby mode was set. That is, if the standby mode was set while the CPU was in native mode, the CPU returns to the native mode upon releasing the standby mode. If the standby mode was set when the CPU was in emulation mode, the emulation mode is resumed. The program execution will be resumed starting from the instruction next to the HALT or HLT instruction.

NOTE: When releasing the standby mode by an input INT signal while the interrupt is disabled, the INT signal must be kept at high level until the instruction next to the HALT/HLT instruction is executed. In other words, the INT signal must remain high level for a lapse of 15 clocks. This applies on the assumption that the instruction

queue has become empty after executing the HALT/HLT instruction, however. If wait states are inserted, the number of inserted wait states must be accordingly added to the 15 clocks.

(2) When interrupt is enabled (EI)

The standby mode is released and the INT interrupt routine in the native mode is started regardless of whether the CPU was in native or emulation mode before the standby mode was set. If the RETI instruction is executed at the end of the INT interrupt routine, the CPU can return to the mode that had been set before the standby mode. The program execution will be resumed starting from the instruction next to the HALT/HLT instruction.

#### 7.4 Releasing Standby Mode by RESET Input

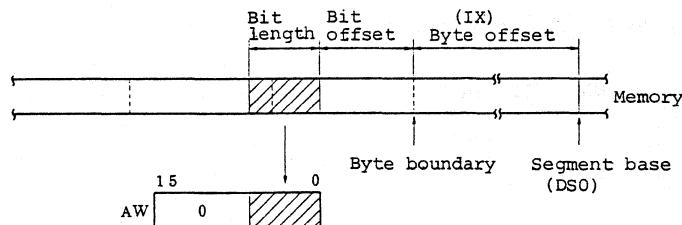

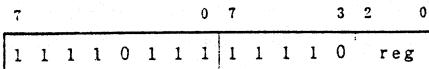

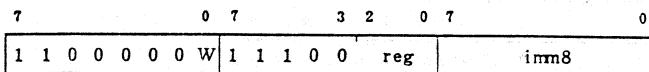

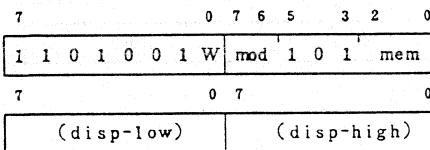

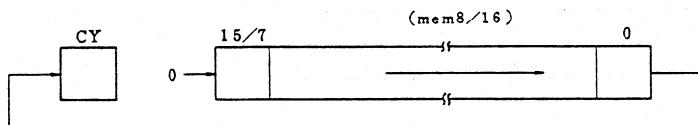

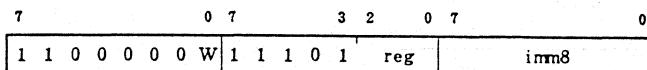

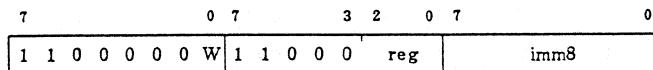

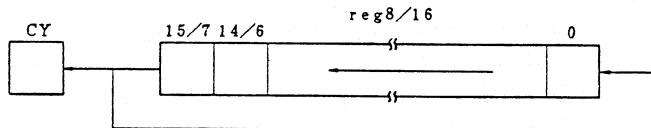

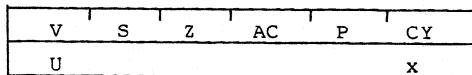

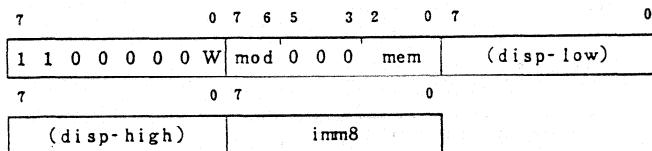

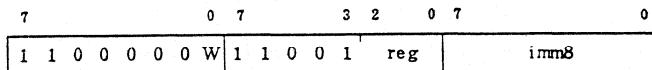

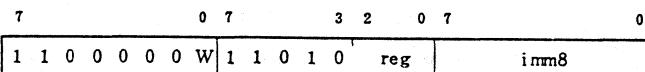

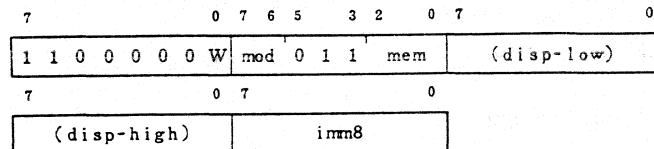

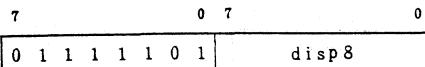

The standby mode is unconditionally released when the RESET input signal becomes active regardless of whether the standby mode was set while the CPU was in native or emulation mode. On releasing the standby mode, a normal CPU reset operation is performed in native mode. The statuses of the CPU that have been retained during the standby mode will be consequently reset. The program execution once stopped by the standby mode therefore cannot be resumed.